# **ACTmap VHDL Synthesis**

Methodology Guide

### Actel Corporation, Sunnyvale, CA 94086

© 1998 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 5579007-1

Release: July 1998

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose.

Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### Trademarks

Actel and the Actel logotype are registered trademarks of Actel Corporation.

Adobe and Acrobat Reader are registered trademarks of Adobe Systems, Inc.

Cadence is a registered trademark of Cadence Design Systems, Inc.

Mentor Graphics is registered trademark of Mentor Graphics, Inc.

Synopsys is a registered trademark of Synopsys, Inc.

UNIX is a registered trademark of X/Open Company Limited.

Verilog is a registered trademark of Open Verilog International.

Viewlogic is a registered trademark and MOTIVE is a trademark of Viewlogic Systems, Inc.

Windows is a registered trademark of Microsoft Corporation in the U.S. and other countries.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

# **Table of Contents**

|   | Introduction vii                     |

|---|--------------------------------------|

|   | Document Organization vii            |

|   | Document Assumptions viii            |

|   | Document Conventions viii            |

|   | Designer Series Manuals ix           |

|   | On-Line Help xi                      |

| 1 | ACTmap Design Flow                   |

|   | Design Flow Illustrated              |

|   | Design Flow Overview                 |

| 2 | Using ACTmap VHDL                    |

|   | VHDL Naming Conventions and Keywords |

|   | Declaring a Circuit                  |

|   | Signals                              |

|   | Operators                            |

|   | Logic Conditions                     |

|   | Repetitive Operations                |

|   | Attributes                           |

|   | Instantiating Cells                  |

|   | Creating Hierarchy                   |

|   | Inferring ACTgen Macros              |

|   | Processes                            |

|   | State Machine Design                 |

|   | Supported Packages                   |

|   | Using Procedures                     |

|   | Limitations                          |

| 3 | Advanced Optimization Techniques     |

|   | ACTmap VHDL Guidelines               |

|   | General Optimization Guidelines      |

|   | State Machine Optimization           |

|   | Setting Design Constraints           |

## Table of Contents

|   | Automatic I/O Insertion              | 53   |

|---|--------------------------------------|------|

|   | 3200DX and 42MX                      | 54   |

|   | Sequential Remapping                 | 54   |

|   | Gated Macros                         | 56   |

|   | Designing for Radiation Environments | 56   |

| A | Using ACTmap in Batch Mode           | 57   |

|   | Invoking ACTmap in Batch Mode        | 57   |

|   | Command Line Format                  | 58   |

|   | Creating a Batch File                | 58   |

|   | Creating a Configuration File        | 59   |

|   | ACTmap Options                       | 60   |

|   | Batch Mode Options Usage Examples    |      |

| В | Product Support                      | 71   |

|   | Actel U.S. Toll-Free Line            |      |

|   | Customer Service                     | . 71 |

|   | Customer Applications Center         | 72   |

|   | Guru Automated Technical Support     | 72   |

|   | Action Facts                         | 72   |

|   | Web Site                             | 73   |

|   | FTP Site                             | 73   |

|   | Electronic Mail                      | 73   |

|   | Worldwide Sales Offices              | 74   |

|   | Glossary                             | 75   |

|   | Index                                | 70   |

# **List of Figures**

| ACTmap Design Flow                             |

|------------------------------------------------|

| Half Adder                                     |

| Half Adder                                     |

| 3 Stage Shift Register                         |

| CLKINT Symbol                                  |

| Full Adder Schematic                           |

| Multiplexer Using an If Statement              |

| Multiplexer using a With or Case Statement     |

| 2 to 1 Multiplexer                             |

| Single Bit D Flip-Flop                         |

| Multi-bit D Latch                              |

| 2 to 1 Multiplexer                             |

| Latch Diagram                                  |

| Single Process FSM                             |

| Mealy FSM                                      |

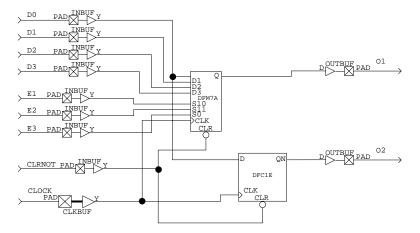

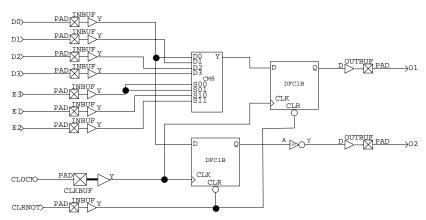

| Library Cells DFC1E and DFM7A before Remapping |

| Library Cells DFC1E and DFM7A after Remapping  |

# Introduction

VHDL is a high-level description language for system and circuit design that supports various abstraction levels, including system design without regard to a specific technology. However, to achieve optimal performance and area from your target device, you must become familiar with the architecture of the device and code your design for the architecture.

The ACTmap VHDL Synthesis Methodology Guide contains information and techniques for using ACTmap VHDL to design an Actel device. This includes information about writing VHDL code for ACTmap, optimization techniques, and sample code. This guide also includes information about using the ACTmap VHDL Synthesis tool in batch mode. Refer to the Designing with Actel manual and the ACTmap online help for information about the ACTmap user interface. Refer to the Actel HDL Coding Style Guide for additional information about HDL coding.

# **Document Organization**

The ACTmap VHDL Synthesis Methodology Guide is divided into the following chapters:

**Chapter 1 - ACTmap Design Flow** describes the design flow for creating Actel designs with the ACTmap VHDL synthesis tool.

**Chapter 2 - Using ACTmap VHDL** describes how to write VHDL for use with the ACTmap VHDL synthesis tool.

**Chapter 3 - Advanced Optimization Techniques** contains information about the optimization features of ACTmap and describes how to implement optimization techniques in a design.

**Appendix A - Using ACTmap in Batch Mode** contains information about using command-line commands and command files in the ACTmap VHDL synthesis tool.

**Appendix B - Product Support** provides information about contacting Actel for customer and technical support.

## Document Assumptions

The information in this guide is based on the following assumptions:

- 1. You have installed the Designer Series software, including ACTmap.

- 2. You are familiar with UNIX workstations and operating systems.

- 3. You are familiar with PCs and Windows operating environments.

- 4. You are familiar with FPGA design software, including design synthesis and simulation tools.

## **Document Conventions**

The following conventions are used throughout this manual:

Information that is meant to be input by the user is formatted as follows:

```

keyboard input

```

The contents of a file is formatted as follows:

```

file contents

```

VHDL code appear as follows, with VHDL keyword in bold:

```

entity actel is

port (

a: in bit;

y: out bit);

end actel;

```

Messages that are displayed on the screen appear as follows:

```

Screen Message

```

The <act\_fam> variable represents an Actel device family. To reference an actual family, substitute the name of the Actel device when you see this variable. Available families are act1, act2 (for ACT 2 and 1200XL devices), act3, 3200dx, 40mx, 42mxand 54sx.

# Designer Series Manuals

The Designer Series software includes printed and on-line manuals. The on-line manuals are in PDF format on the CD-ROM in the "/doc" directory. These manuals are also installed onto your system when you install the Designer software. To view the on-line manuals, you must have Adobe® Acrobat Reader® installed. Actel provides Reader on the Designer Series CD-ROM.

The Designer Series includes the following manuals, which provide additional information on designing Actel FPGAs:

Designing with Actel. This manual describes the design flow and user interface for the Actel Designer Series software, including information about using the ACTgen Macro Builder and ACTmap VHDL Synthesis software.

Actel HDL Coding Style Guide. This guide provides preferred coding styles for the Actel architecture and information about optimizing your HDL code for Actel devices.

ACTmap VHDL Synthesis Methodology Guide. This guide contains information, optimization techniques, and procedures to assist designers in the design of Actel devices using ACTmap VHDL.

Silicon Expert User's Guide. This guide contains information and procedures to assist designers in the use of Actel's Silicon Expert tool.

Cadence® Interface Guide. This guide contains information and procedures to assist designers in the design of Actel devices using Cadence CAE software and the Designer Series software.

*Mentor Graphics* \*\* *Interface Guide*. This guide contains information and procedures to assist designers in the design of Actel devices using Mentor Graphics CAE software and the Designer Series software.

$MOTIVE_{TM}$  Static Timing Analysis Interface Guide. This guide contains information and procedures to assist designers in the use of the MOTIVE software to perform static timing analysis on Actel designs.

*Synopsys® Synthesis Methodology Guide.* This guide contains preferred HDL coding styles and information and procedures to assist designers in the design of Actel devices using Synopsys CAE software and the Designer Series software.

#### Introduction

Viewlogic® Powerview Interface Guide. This guide contains information and procedures to assist designers in the design of Actel devices using Powerview CAE software and the Designer Series software.

Viewlogic Workview® Office Interface Guide. This guide contains information and procedures to assist designers in the design of Actel devices using Workview Office CAE software and the Designer Series software.

VHDL Vital Simulation Guide. This guide contains information and procedures to assist designers in simulating Actel designs using a Vital compliant VHDL simulator.

*Verilog® Simulation Guid*e. This guide contains information and procedures to assist designers in simulating Actel designs using a Verilog simulator.

Activator and APS Programming System Installation and User's Guide. This guide contains information about how to program and debug Actel devices, including information about using the Silicon Explorer diagnostic tool for system verification.

Silicon Sculptor User's Guide. This guide contains information about how to program Actel devices using the Silicon Sculptor software and device programmer.

*Silicon Explorer Quick Start.* This guide contains information about connecting the Silicon Explorer diagnostic tool and using it to perform system verification.

Designer Series Development System Conversion Guide UNIX Environments. This guide describes how to convert designs created in Designer Series versions 3.0 and 3.1 for UNIX to be compatible with later versions of Designer Series.

Designer Series Development System Conversion Guide Windows Environments. This guide describes how to convert designs created in Designer Series versions 3.0 and 3.1 for Windows to be compatible with later versions of Designer Series.

FPGA Data Book and Design Guide. This guide contains detailed specifications on Actel device families. Information such as propagation delays, device package pinout, derating factors, and power calculations are found in this guide.

*Macro Library Guide*. This guide provides descriptions of Actel library elements for Actel device families. Symbols, truth tables, and pin loading are included for all macros.

# On-Line Help

The Designer Series software comes with on-line help. On-line help specific to each software tool is available in Designer, ACTgen, ACTmap, Silicon Expert, and APSW.

# **ACTmap Design Flow**

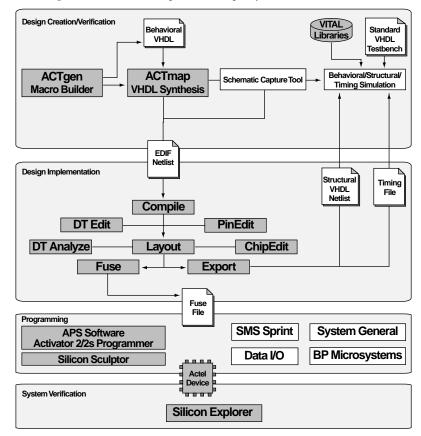

This chapter illustrates and describes the design flow for creating Actel designs using the ACTmap VHDL synthesis tool and third party tools.

# Design Flow Illustrated

Figure 1-1 illustrates the design flow for creating an Actel device using the Designer Series, ACTmap, and 3rd party CAE software<sup>1</sup>.

Figure 1-1. ACTmap Design Flow

<sup>1.</sup> Actel-specific utilities/tools are denoted by the grey boxes in Figure 1-1.

# Design Flow Overview

The ACTmap design flow has four main steps; design creation/verification, design implementation, programming, and system verification. These steps are described in detail in the following sections.

### Design Creation/ Verification

During design creation/verification, a design is captured in an RTL-level (behavioral) VHDL source file. After capturing the design, behavioral simulation of the VHDL file can be performed to verify that the VHDL code is correct. The code is then synthesized into an Actel gate-level (structural) VHDL netlist using ACTmap. After synthesis, structural simulation of the design can be performed. Finally, an EDIF netlist is generated for use in Designer or a third party CAE tool. A structural VHDL netlist is also generated for timing simulation.

#### VHDL Design Source Entry

Enter your VHDL design source using a text editor or a context-sensitive VHDL editor. Your VHDL design source can contain RTL-level constructs as well as instantiations of structural elements, such as ACTgen macros. Refer to Chapter 2, "Using ACTmap VHDL" on page 5, for information about ACTmap VHDL coding techniques.

#### **Behavioral Simulation**

Perform a behavioral simulation of your design before synthesis. Behavioral simulation verifies the functionality of your VHDL code. Typically, unit delays are used and a standard VHDL test bench can be used to drive simulation. Refer to the documentation included with your simulation tool for information about performing behavioral simulation.

#### Synthesis

After you have created your behavioral VHDL design source, create a project in ACTmap and synthesize your design before placing and routing it in Designer. Synthesis transforms the behavioral VHDL file into a gate-level netlist and optimizes the design for a target technology. Refer to the *Designing with Actel* manual for information about synthesizing a design in ACTmap.

#### **EDIF Netlist Generation**

After you have created, synthesized, and verified your design, you must generate an EDIF netlist for place and route in Designer. ACTmap also can be used to create symbols and wire files for use in Viewlogic tools. Most third party CAE tools can also import the EDIF netlist as a block for use in a schematic capture tool. Refer to the Actel Interface Guides and the documentation included with your CAE tools for information about importing EDIF blocks.

This EDIF netlist is also used to generate a structural VHDL netlist. Refer to the *Designing with Actel* manual for information about generating an EDIF netlist from ACTmap.

#### Structural VHDL Netlist Generation

Generate a structural VHDL netlist from your EDIF netlist for use in structural and timing simulation by exporting it from ACTmap. Refer to the *Designing with Actel* manual for information about generating a structural netlist from ACTmap.

#### Structural Simulation

Perform a structural simulation of your design before placing and routing it. Structural simulation verifies the functionality of your post-synthesis structural VHDL netlist. Default unit delays included in the compiled Actel VITAL libraries are used for every gate. Refer to the documentation included with your simulation tool for information about performing structural simulation.

## Design Implementation

During design implementation, a design is placed and routed using Designer. Additionally, static timing analysis can be performed in Designer with the DT Analyze tool. After place and route, post-layout (timing) simulation is performed.

#### Place and Route

Use Designer to place and route your design. Make sure to specify GENERIC as the Edif Flavor and VHDL as the Naming Style when importing the EDIF netlist into Designer. Refer to the *Designing with Actel* manual for information about using Designer.

#### Chapter 1: ACTmap Design Flow

#### **Timing Analysis**

Use the DT Analyze tool in Designer to perform static timing analysis on your design. Refer to the *Designer with Actel* manual for information on using DT Analyze.

#### Timing Simulation

Perform a timing simulation of your design after placing and routing it. Timing simulation verifies that the design meets timing requirements. Timing simulation requires information extracted from Designer, which overrides default unit delays in the compiled Actel VITAL libraries. Refer to the documentation included with your simulation tool for information about performing timing simulation and the *Designing with Actel* manual for information about extracting timing information from Designer.

## **Programming**

Program a device with programming software and hardware from Actel or a supported 3rd party programming system. Refer to the *Designing with Actel* manual and the *Activator and APS Programming System Installation and User's Guide* or *Silicon Sculptor User's Guide* for information about programming an Actel device.

### System Verification

You can perform system verification on a programmed device using the Actel Silicon Explorer diagnostic tool. Refer to the *Activator and APS Programming System Installation and User's Guide* or *Silicon Explorer Quick Start* for information about using the Silicon Explorer.

# **Using ACTmap VHDL**

This chapter provides descriptions and examples of how to write VHDL for use with the ACTmap VHDL synthesis tool. This includes information about VHDL naming conventions and keywords, about declaring circuits and signals in VHDL, and a description of supported operators. Also included is information about using logic conditions and repetitive operations, assigning attributes, and instantiating cells.

Other sections include how to create hierarchical designs for ACTmap, how to infer ACTgen macros, and information about writing processes. State machine design is described and guidelines for using procedures are also given. Finally, supported packages and limitations are listed.

# VHDL Naming Conventions and Keywords

There are naming conventions you must follow when writing VHDL code. Additionally, VHDL has reserved words that cannot be used for signal or entity names. This section lists the naming conventions and reserved keywords for each.

### Naming Conventions

The following naming conventions apply to VHDL designs:

- VHDL is not case sensitive.

- Two dashes "--" are used to begin comment lines.

- Names can use alphanumeric characters and the underscore "\_" character.

- Names must begin with an alphabetic letter.

- You may not use two underscores in a row, or use an underscore as the last character in the name.

- Spaces are not allowed within names.

- Object names must be unique. For example, you cannot have a signal named A and a bus named A(7 downto 0).

- An entity cannot have the same name as an Actel Library macro.

## **Keywords**

The following is a list of the VHDL reserved keywords that cannot be used for signal or entity names:

| abs           | downto   | library | postponed | subtype    |

|---------------|----------|---------|-----------|------------|

| access        | else     | linkage | procedure | then       |

| after         | elsif    | literal | process   | to         |

| alias         | end      | loop    | pure      | transport  |

| all           | entity   | map     | range     | type       |

| and           | exit     | mod     | record    | unaffected |

| architecture  | file     | nand    | register  | units      |

| array         | for      | new     | reject    | until      |

| assert        | function | next    | rem       | use        |

| attribute     | generate | nor     | report    | variable   |

| begin         | generic  | not     | return    | wait       |

| block         | group    | null    | rol       | when       |

| body          | guarded  | of      | ror       | while      |

| buffer        | if       | on      | select    | with       |

| bus           | impure   | open    | severity  | xnor       |

| case          | in       | or      | shared    | xor        |

| component     | inertial | others  | signal    |            |

| configuration | inout    | out     | sla       |            |

| constant      | is       | package | sra       |            |

| disconnect    | label    | port    | srl       |            |

|               |          |         |           |            |

# Declaring a Circuit

A circuit description consists of the interface defining the signal connections of the circuit and a description of the circuit's behavior or composition. The interface is referred to as an entity and the signal connections are ports. The section of code that defines the entity behavior or composition is referred to as the architecture. The entity in VHDL is equivalent to a symbol. The architecture is equivalent to a schematic.

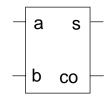

## Entity Description

An entity consists of the entity name, the names of entity's ports, the direction of the ports (input, output, etc.), and a VHDL signal type for each of the ports. Below is an example entity description for a half adder, illustrated in Figure 2-1.

Figure 2-1. Half Adder

```

entity halfadder is

port (a, b: in bit;

s, co: out std_logic);

end halfadder;

```

# Architecture Description

The behavior or composition of the entity is described in the architecture section of code. The level of the VHDL description of the architecture can be behavioral, register transfer level (RTL), or structural.

A behavioral description describes how the system behaves in response to input signals without regard for hardware implementation.

An RTL description defines the circuit behavior, much like a detailed block diagram describes traditional logic design. Clock and reset signals are defined, and data busses and storage devices (registers, counters, memory, etc.) have specific numbers of bits assigned. However, the level of abstraction used to describe the logic functions is higher than the gate-level details of a conventional schematic.

A structural description is used in the same manner as a netlist.

### Chapter 2: Using ACTmap VHDL

The structure of the design is described by components interconnected by signals. Regardless of the VHDL description level, the syntax of the architecture must have a type and an entity association, as in the following example:

```

architecture behavioral of example is

... signals and constants are declared...

begin

... lines of code describing the behavior of entity example...

end example;

```

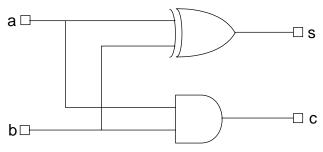

Below is an architectural description of the functionality of a half adder entity. The half adder is illustrated in Figure 2-2.

Figure 2-2. Half Adder

```

architecture behavioral of halfadder is

begin

s <= a xor b;

c <= a and b;

end behavioral;</pre>

```

# Signals

Signal declarations are made in the declaration section of the architecture. This is the section of code that appears after the architecture type and entity association have been defined and before the begin statement. Constants are also defined in the declaration section, often after the signals are declared.

As in a physical hardware system, signals can be single bits, such as a clock or a reset, or they can be busses of a specified width. All signals are declared with both a name and a data type. VHDL by itself does not predefine characteristics of signals such as logic states or driving strengths. Instead it makes provisions for doing so by means of VHDL files grouped together into packages and libraries, which are normally shipped with VHDL simulators or synthesis tools. This section lists the data types that ACTmap supports.

## Enumerated Types

Types that have a fixed number of unique states are called enumerated types. You can choose to use one of the standard types or define your own.

#### Bit and Boolean

The bit and boolean types are standard enumerated types defined as part of ACTmap VHDL and have two states each.

• bit can be '0' or '1'

signal a: bit;

boolean can be true or false

signal a: boolean;

#### **User-Defined**

Enumerated types are often defined by the user for a specific purpose, such as declaring the states of a state machine. Each state of the defined type must be a unique identifier. The enumerated type must be defined using the following syntax before a signal can be declared of that type.

```

type speedtype is (stop, fast, faster);

```

Once a signal of type speedtype is defined, it can only contain one of the three values. Below is an example of a signal defined as type speedtype:

```

signal speed: speedtype;

```

The following example shows how user defined types are defined and used.

```

architecture behavioral of drive is

signal light: bit_vector(0 to 1);

type speedtype is (stop, fast, faster);

signal speed: speedtype;

constant red: bit_vector(0 to 1) := "00";

constant yellow: bit_vector(0 to 1) := "01";

constant green: bit_vector(0 to 1) := "10";

begin

with light select

speed <= stop when red;

fast when green,

faster when others;

end behavioral;</pre>

```

## Std\_Logic

Two state types are often not sufficient for most simulations. For unknown values and varying signal strengths, a 9-state logic system, often referred to as MVL9, was adopted as a standard by IEEE. This standard enumerated type is called std\_logic. The following states are defined:

- U for unitialized

- X for unknown

- Z for tri-state

- · W for weak strength

- H for high (resistive) used for open collector outputs

- L for low (resistive) used for open emitter outputs

- - for don't care

Note: During VHDL compilation, ACTmap treats '0' and 'L' as low, '1' and 'H' as high, and 'U', 'X', 'W' and '-' as don't care.

## Std Ulogic

Actel does not recommend using the std\_ulogic data type. ACTmap, ACTgen, and Designer do not have the capability to write VHDL netlists using the std\_ulogic data type. All VHDL netlists are written using the std\_logic data type. Test benches written using the std\_ulogic data types generally do not work with gate-level VHDL netlists created by the Designer Series tools.

#### **Vectors**

Busses or multibit signals are referred to as vectors. The data types bit and std\_logic are definable as vectors. When vectors are defined, a range for the vector array must be declared. The range can be either ascending or descending. For an ascending range, the most significant bit is on the left and is defined using the "to" keyword as follows:

signal databus: std\_logic\_vector(0 to 7);

| Ø 1 2 | 3 | 4 | 5 | 6 | 7 |  |

|-------|---|---|---|---|---|--|

|-------|---|---|---|---|---|--|

### Chapter 2: Using ACTmap VHDL

For descending range, the most significant bit is on the right, and is defined using the "downto" keyword as follows:

signal databus: std\_logic\_vector(7 downto 0);

To use the entire vector, use the name of the vector as shown:

databus

Individual bits of a bus or register are used as shown:

A portion of a bus or register is referred to as a slice and is used as shown:

databus(7 downto 3)

Databus (7 downto 3) = "slice"

Note: The "to" or "downto" statement of the slice must agree with the to or downto statement of the vector declaration.

### Integer Types

An integer type defines the set of integer values in its range. When designing arithmetic behavior, it is very helpful to work with integer types. VHDL pre-defines an integer type called "integer" that covers a range of integer values that can be represented in two's complement with 32 bits:

```

signal s32_int: integer;

```

An object can also be defined to be a sub-range of an integer:

```

signal s4_int: integer range 0 to 15;

```

#### **Constants**

Similar to a signal declaration, constants can be declared and given names. The following is an example of a constant declaration:

```

constant yellow: bit_vector := "01";

```

In this example, the name of the constant is yellow and it is a bit\_vector whose value is always "01." The constant declaration uses a similar syntax to the signal declaration with the addition of the ":=" and the assigned value of the constant. Binary values of vectors are always enclosed in double quotes as shown, and are referred to as bit string literals. You can, but you do not need to, specify how many bits are in the constant with a to or downto statement.

# **Operators**

The standard logical and arithmetic operations that are supported by ACTmap are shown in Table 2-1.

Table 2-1. Supported Arithmetic Operators

| Туре       | Symbol | Operation                | Operand Type                             |

|------------|--------|--------------------------|------------------------------------------|

| Arithmetic | +      | addition                 | integer, bit_vector,<br>std_logic_vector |

|            | -      | subtraction              | integer, bit_vector,<br>std_logic_vector |

|            | *      | multiplication           | integer, bit_vector, std_logic_vector    |

| Logical    | and    | logical and              | bit, boolean                             |

|            | or     | logical or               | bit, boolean                             |

|            | nand   | logical nand             | bit, boolean                             |

|            | nor    | logical nor              | bit, boolean                             |

|            | xor    | logical excusive-or      | bit, boolean                             |

|            | not    | logical compliment       | bit, boolean                             |

| Relational | =      | equal                    | any type                                 |

|            | /=     | not equal                | any type                                 |

|            | <      | less than                | any type                                 |

|            | >      | greater than             | any type                                 |

|            | <=     | less than or equal       | any type                                 |

|            | >=     | greater than or<br>equal | any type                                 |

| Туре          | Symbol | Operation     | Operand Type                                       |

|---------------|--------|---------------|----------------------------------------------------|

| Concatenation | &      | concatenation | bit, bit_vector,<br>std_logic,<br>std_logic_vector |

Table 2-1. Supported Arithmetic Operators (Continued)

The following guidelines should be used when using the operators in your VHDL design:

• Parentheses must be included where the intended function may be ambiguous. The expression "a and b or not (c)" could be interpreted as "a and (b or not(c))" or "(a and b) or not(c)", which are not equivalent. For example:

```

y <= (a and b) or not (c);

```

• The following example would mean a signal assignment without the if keyword. Within the if statement, the operator means less than or equal.

```

if databus_1 <= databus_2 then</pre>

```

# Logic Conditions

The various means of testing for logic conditions include the if, when, select, and case statements. If and case statements are used only in processes. Select and when statements are used only outside of processes.

## If Statement

An if statement is a conditional statement that may only be used in a process. The syntax for an if statement is as follows:

```

if condition then

some action;

elsif condition 2 then

```

### Chapter 2: Using ACTmap VHDL

```

some action;

end if;

```

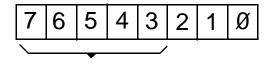

The following is an example of an if-then-else statement that synthesizes a 3 stage shift register and is illustrated in Figure 2-3:

Figure 2-3. 3 Stage Shift Register

```

if (reset = '1') then

a <= '0';

b <= '0';

c <= '0';

elsif (clock'event and clock = '1') then

a <= shiftin;

b <= a;

c <= b;

end if;</pre>

```

### When Statement

A when statement is a conditional state assignment that synthesizes as combinatorial logic. The syntax for a when statement is as follows:

```

signal <= 'value' when condition

else 'value';</pre>

```

Below is an example of a when statement that synthesizes as an N bit "greater than" comparator:

```

signal <= '1' when databus > register

else '0';

```

### Select Statement

A select statement is a selected signal assignment that synthesizes into combinatorial logic. The syntax for a select statement is as follows:

```

with signal select

target output <=waveform 1

when condition 1,

waveform 2 when condition 2,

waveform N when condition N;</pre>

```

Below is an example of a select statement that synthesizes as a four to one multiplexer controlled by "sel," a two-bit control signal, whereby "y" is switched to one of the four data lines:

```

with sel select

y <= a when "00",

b when "01",

c when "10",

d when "11";</pre>

```

#### Case Statement

A case statement is a selected signal assignment within a process. The syntax for a case statement is as follows:

```

case state is

when condition 1 => target output <= waveform 1;

when condition 2=> target output <= waveform 2;

when condition N=> target output <= waveform N;

when others => target output <= default waveform;

end case;</pre>

```

Below is an example of a case statement that synthesizes the same logic as the select code above when used within an unclocked process:

```

case sel is

when "00" => y <= a;

when "01" => y <= b;

when "10" => y <= c;

when others => y <= d;

end case;</pre>

```

#### Chapter 2: Using ACTmap VHDL

Case statements must specify all possible cases. The "when others =>" statement should be added to VHDL case statements using std\_logic data types. The following error message is displayed in ACTmap if all cases are not specified in a case statement:

```

ERROR: (VHP_0812). Line 29. A value is missing in case

```

# Repetitive Operations

Repetitive structures are declared with a generate statement.

#### If-Generate Statement

The if-generate statement is supported for static (non-dynamic) conditions.

```

loop label: if condition generate

loop actions;

end generate;

```

#### For-Generate Statement

The for-generate statement is supported for static (non-dynamic) conditions.

```

loop label: for variable in start condition to end condition

generate

loop actions;

end generate;

```

## For-Generate Loop

For component instantiations, function or procedure calls inside a forgenerate loop, a block statement has to be used inside the loop to be accepted by the ACTmap VHDL Compiler. The following is an example of a for generate loop inside a block statement:

```

entity example is

...

end example;

architecture arch of example is

component small

```

```

end component;

...

for all: small use entity work.small(arch);

begin

loop1: for i in 0 to 3 generate

begin block statement

block1: block

begin

instance1: small port map ( a(i), b(i), s(i) );

end block; -this line is added

end generate loop1;

end arch;

```

## **Attributes**

The ACTmap VHDL Compiler uses the "donttouch" attribute to control synthesis of the described circuit. The "donttouch" attribute directs ACTmap not to optimize a given instance. Before the attribute can be used, it must first be declared with a type. The attribute can only be attached to instances of previously optimized macros or modules.

The syntax for declaring the donttouch attribute is as follows:

```

attribute donttouch : string;

```

The syntax for attaching the "donttouch" attribute is as follows:

```

attribute donttouch of instance label: label is "attribute

value";

```

Below is an example of adding the value true to the donttouch attribute:

```

for instance actgen_1:

attribute donttouch : string;

attribute donttouch of actgen_1: label is "true";

```

Note: The value of the attribute is not important in this case.

# Instantiating Cells

In order to instantiate an entity into a VHDL description, you must first declare a component for it. If you use a component instantiation in your VHDL design, ACTmap tries to find the definition of that component. There are three possibilities for defining an instantiated cell:

- 1. The component is a cell in the specified Actel macro library.

- 2. The component has a matching entity in the VHDL source file.

- 3. The component has no definition.

### **Library Macros**

Components in the Actel macro library are considered black boxes during synthesis since there is no entity/architecture description for them. Actel library cells defined in the VHDL code are not optimized in VHDL Compiler, but are treated as black boxes.

When the optimized EDIF netlist is written, the contents for each macro is completed. An added benefit is that the time needed for optimization of the whole circuit can be reduced, since ACTmap does not have to optimize the implementation of the dedicated functions.

Note: Components found in the specified Actel macro library do not need component statements. ACTmap maintains a compiled version of these component statements.

The following example, illustrated in Figure 2-4, instantiates the ACT 3 "clkint" macro:

Figure 2-4. CLKINT Symbol

clkint\_1: clkint port map (signal\_a, signal\_y);

Port mapping may be positional as in the example or it may be done by name. In positional mapping, the signals are associated to the ports by the order the ports are declared in the component declaration. In name mapping, explicitly specify the name of the port followed by the signal tied to it. For name mapping, use any port order. Positional and name mapping are functionally identical. The following is an example of a component instantiation for the clkint macro using name mapping:

```

clkint_1: clkint port map (a => signal_a, y => signal_y);

```

#### ACTgen Macros

Use the following procedure to instantiate an ACTgen macro into a VHDL description:

- 1. Invoke ACTgen.

- 2. Select the family, macro type, and macro options.

- **3. Generate your macro as a VHDL description.** Make sure you specify VHDL as the Netlist/CAE Format when generating the macro.

- 4. Add a component declaration in the entity of your VHDL description for the macro. For example:

5. Instantiate the macro into your VHDL description using a port map statement. For example:

```

ul : cnt4 port map (signaldata => data, signalenable =>

enable, signalsload => sload, signalaclr => aclr,

signalclock =>clock, signalq => q);

```

**6. Compile your VHDL description.** Refer to "Implementing a Hierarchical Project" in the *Designing with Actel* manual for information about compiling a VHDL description in ACTmap.

Refer to the *Designing With Actel* manual or the ACTgen on-line help for information about using ACTgen.

# Creating Hierarchy

Up to this point, the discussions have focussed on logic circuits that most likely would be part of a single VHDL entity or functional block of logic. These blocks should generally be limited in size so that they can be synthesized and simulated relatively quickly. Most FPGA designs consist of multiple entities or logic blocks. Hierarchical designs can be created using a structural VHDL description.

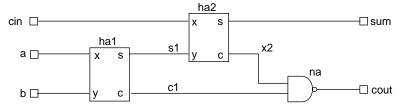

Consider the schematic of a full adder that consists of two half adders, shown in Figure 2-5.

Figure 2-5. Full Adder Schematic

This design uses two separate instances of half adders, designated as components "ha1" and "ha2." Like any other schematic, the actual signals connected to the component pins may have different names than the individual entity's port names. Without this capability, you would not be able to use an entity more than once in a design.

The following is the entity and architecture description for the half adder logic block:

```

entity halfadder is

port (x, y: in bit;

s, c: out bit);

end halfadder ;

architecture behavioral of halfadder is

begin

s <= x xor y;

c <= x and y;

end behavioral;</pre>

```

The architecture of the full adder, top-level logic block, is a structural VHDL interconnection of the entity components and signals. The architecture consists of two parts: the declaration and instantiation sections.

#### **Declaration Section**

The declaration section includes Signal declarations for signals such as "c1" that are internal to the full adder entity, component declarations for the "parts" used, constant declarations, if needed, and configuration declarations to bind all instances to the desired architecture description.

#### Instantiation Section

The instantiation section includes Component Instances, such as "ha1," "ha2," etc., with their specific signal connections defined in a port map declaration.

The entity and architecture for a full adder are as follows:

```

architecture structural of fulladder is

signal c1, c2, s1: bit;

component halfadder

port (

x, y: in bit;

s, c: out bit);

end component;

begin

hal: halfadder port map (a, b, s1, c1);

ha2: halfadder port map (x=>cin, y=>s1, s=>sum, c=>c2);

cout <= c1 nand c2;

end structural;</pre>

```

Note: Notice that instance "ha1" was instantiated using positional mapping, and instance "ha2" was instantiated using name mapping.

## Inferring ACTgen Macros

Macros such as counters, multiplexers, adders and subtractors can be described in your VHDL code and created using the ACTgen Macro Builder. This section describes how to infer different types of ACTgen macros.

#### Counters

ACTmap recognizes counters from the VHDL specification and calls ACTgen to generate an optimized counter for the final design. The following guidelines apply to the previous example for inferring a counter:

- The data\_load and the data signals can be of type bit\_vector, std\_logic\_vector, or unsigned.

- The reset, sload, and updown signals are optional. However, when used they must be a simple name comparison to '1' or '0'.

- The data must be set to a constant value upon reset.

- The count may only increment by one.

- An ACTgen macro will not be inferred correctly if the count enable and asynchronous load signals both exist.

Counters, including those requiring an asynchronous reset, a synchronous load, count enable, and up-down count facilities, can be inferred with the following general counter template:

```

architecture template of gencount is

signal data: std_logic_vector (msb downto 0);

begin

counter_1: process (clk, reset, sload)

if ( reset = '0' ) then

data <= "00000000";

elsif ( clk'event and clk = '1' ) then

if (load = '0') then

data <= load_data;

elsif (updown = '1') then

data <= data + '1' ;

data <= data - '1';

end if;

end if;

end process counter_1;

end template;

```

#### Multiplexers

ACTmap recognizes multiplexers from the VHDL specification and calls ACTgen to generate optimized macros for the final design. From 2 to 32 inputs may be multiplexed with busses of up to 24 bits for every input in ACT 1 and 40MX and busses up to 32 bits for every input in all other device families. There are three templates that may be used to infer multiplexers in VHDL and generate them with the ACTgen Macro Builder.

The following guidelines apply to the examples for inferring a multiplexer:

- If more than half of the data inputs are constant values, the macro block is not inferred, because simplifications are possible in the netlist due to this constant value.

- Although std\_logic\_vector is allowed in the template, the "-" (don't care value) is not considered.

- When using "if" or "case" statements to infer a multiplexer, some values of the selector may be unspecified (no "else" or no "when others" statement). An extra latch is generated to keep the value if the selector reaches these unspecified values.

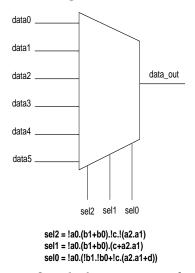

#### Multiplexer Using an If Statement

In this example, a 6 to 1 multiplexer, illustrated in Figure 2-6, is generated by ACTgen. Some logic is generated and connected to the selection port of the multiplexer in order to select the correct inputs according to the values of signals "a," "b," "c," and "d."

Figure 2-6. Multiplexer Using an If Statement

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity genmx1 is

port (

data0: in

bit_vector(11 downto 0);

bit_vector(11 downto 0);

datal: in

data2: in

bit_vector(11 downto 0);

data3: in

bit_vector(11 downto 0);

data4: in

bit_vector(11 downto 0);

data5: in

bit_vector(11 downto 0);

data_out: out bit_vector(11 downto 0);

a: in bit_vector(2 downto 0);

b: in bit_vector(1 downto 0);

c: in bit;

d: in

bit);

end genmx1;

```

```

architecture template of genmx1 is

begin

mux: process

(a,b,c,d,data0,data1,data2,data3,data4,data5)

begin

if (a(0) = '0') then

data_out <= data0;</pre>

elsif (b = '0') then

data_out <= data1;</pre>

elsif (c = '1') then

data_out <= data2;

elsif ( a(2 \text{ downto } 1) = "11" ) then

data_out <= data3;</pre>

elsif (d = '0') then

data_out <= data4;</pre>

else

data_out <= data5;</pre>

end if;

end process mux;

end template;

```

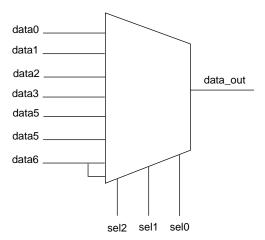

#### Multiplexer Using a With Statement

In this example, an 8 to 1 multiplexer, illustrated in Figure 2-7, is generated by ACTgen. The "sel" signals are connected to the selection ports directly.

Figure 2-7. Multiplexer using a With or Case Statement

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity genmx2 is

port (

data0: in

bit_vector(11 downto 0);

data1: in bit_vector(11 downto 0);

data2: in bit_vector(11 downto 0);

data3: in bit_vector(11 downto 0);

data4: in bit_vector(11 downto 0);

data5: in

bit_vector(11 downto 0);

data6: in

bit_vector(11 downto 0);

data_out: out bit_vector(11 downto 0);

sel: in

bit_vector(2 downto 0));

end genmx2;

architecture template of genmx2 is

begin

with sel select

data_out <= data6 when "110" | "111",

data2 when "010";

datal when "001";

data5 when "101";

data0 when "000";

data3 when "011";

data4 when others;

end template;

```

#### Multiplexer Using a Case Statement

In this example, an 8 to 1 multiplexer, illustrated in Figure 2-7, is generated by ACTgen. The "sel" signals are connected to the selection ports directly.

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity genmx3 is

port (

data0: in

bit_vector(11 downto 0);

data1: in

bit_vector(11 downto 0);

data2: in

bit_vector(11 downto 0);

data3: in

bit_vector(11 downto 0);

data4: in

bit_vector(11 downto 0);

data5: in

bit_vector(11 downto 0);

```

```

data6: in bit_vector(11 downto 0);

data_out: out bit_vector(11 downto 0);

bit_vector(2 downto 0));

end genmx3;

architecture template of genmx3 is

begin

mux: process (data0,data1,data2,data3,data4,data5,data6,sel)

begin

case sel is

when "110" | "111" =>

data_out <= data6;</pre>

when "010"=>

data_out <= data2;

when "001"=>

data_out <= data1;</pre>

when "101"=>

data_out <= data5;

when "000"=>

data_out <= data0;

when "011"=>

data_out <= data3;</pre>

when others =>

data_out <= data4;

end case;

end process;

end template;

```

#### Adders and Subtractors

ACTmap recognizes adders and subtractors from the VHDL specification and calls ACTgen to generate optimized macros for the final design. The following guidelines apply when inferring adders and subtractors:

- The data\_a, data\_b, and data\_out signals can be of type bit\_vector, std\_logic\_vector, or unsigned.

- The output data, "data\_out," must have a size equal to the input data busses, "data\_a" and "data\_b."

Adders and subtractors can be inferred by using the following subtractor example (to infer an adder, change the "-" operator to "+"):

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

```

```

entity gensub is

generic ( msb : integer := 7);

port (

data_a: in std_logic_vector ( msb downto 0);

data_b: in std_logic_vector ( msb downto 0);

data_out: inout std_logic_vector ( msb downto 0));

end gensub;

architecture template of gensub is

begin

data_out <= data_a - data_b;

end template;</pre>

```

#### **Multipliers**

ACTmap recognizes multipliers from the VHDL specification and calls ACTgen to generate optimized macros for the final design. The following guidelines apply when inferring multipliers:

- the "A" and "B" signals can be of type bit\_vector, std\_logic\_vector, or unsigned.

- An ACTgen macro is inferred when "A \* B" is found (if both "A" and "B" are not a constant).

- An ACTgen macro is only inferred if the following constraints are met; 2 <= WidthA <= 29, 2 <= WidthB <= 29, and WidthA + WidthB <= 32.</li>

- If WidthA < 2 or WidthB < 2, ACTmap does not work.

- If WidthA > 29, or WidthB > 29, or WidthA + WidthB > 32, which is beyond the ACTgen limitation, ACTmap does not infer an ACTgen macro. Library based synthesis is employed instead.

- Although in ACTgen WidthA must be greater than or equal to WidthB, this limitation does not apply when inferring a multiplier.

Multipliers can be inferred by using the following example:

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity testmultiplier is

```

# Incrementers and Decrementers

ACTmap recognizes incrementers and decrementers from the VHDL specification and calls ACTgen to generate optimized macros for the final design. The following guidelines apply when inferring incrementers and decrementers:

- The "a" and "p" signals can be of type bit\_vector, std\_logic\_vector, or unsigned.

- An ACTgen macro is inferred when  $p \le a + 1$ ,  $p \le a 1$ ,  $a \le a + 1$ , and  $a \le a 1$ , when the width of "a" and "p" is  $1 \le a 1$ .

- An ACTgen macro is inferred when "a + 1" or "a 1" is found in a top level VHDL specification, function, procedure, and hierarchy model.

Incrementers and decrementers can be inferred by using the following example:

```

else

p <= a - 1;

end if;

end process;

end template;</pre>

```

#### **Processes**

Processes are sections of sequentially executed statements. While in the dataflow syntax, all statements are executed concurrently. In a process, the order of the statements does not matter. Processes resemble the sequential coding style of high-level programming languages.

A process can be called from the dataflow section of VHDL code. Each process is a sequentially executed program, but all processes run concurrently. Processes communicate with each other via signals that are declared in the declaration section of the architecture. The signals that the process waits for are included in the sensitivity list of the process. During the normal flow of a VHDL simulation, the process waits for a change to occur on one of the signals in the sensitivity list. It executes the statements between the begin and the end of the process.

Processes are labeled and use the following syntax:

```

label: process (sensitivity list)

begin

... lines of code describing the behavior of the process ...

end process label;

```

The actions described in the process can be of two forms; a clocked process that is synthesized into clocked or sequential logic, or an unclocked process that produces combinatorial logic. Clocked processes always include the clock signals in the sensitivity list.

There are two types of expressions that can be used to infer clocked logic, a 'event attribute or a function call. For example:

```

(clk'event and clk='1') --rising edge 'event attribute

(clk'event and clk='0') --falling edge 'event attribute

rising_edge(clock) --rising edge function call

falling_edge(clock) --falling edge function call

```

A clock signal cannot use the rising edge procedure if it has been defined as type bit. In order to use the rising edge procedure, the clock must be defined as type std\_logic. The following error message is displayed in ACTmap if a rising edge is not properly defined:

```

ERROR: (VHP_0808). Line 17. rising_edge can not have such operands in this context.

```

#### Inferring Multiplexers

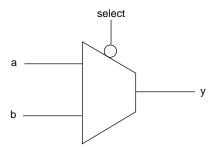

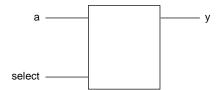

The following example, illustrated in Figure 2-8, infers a 2 to 1 multiplexer:

Figure 2-8. 2 to 1 Multiplexer

```

architecture behavioral of mx2 is

begin

mx2_1: process (a, b, select)

begin

if (select = '0') then

y <= a;

else

y <= b;

end if;

end process mx2_1;

end behavioral;</pre>

```

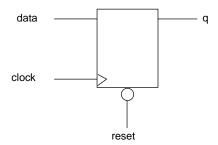

#### Inferring Flip-Flops

The following example, illustrated in Figure 2-9, infers a single bit D flip-flop with an active low asynchronous clear:

Figure 2-9. Single Bit D Flip-Flop

```

architecture behavioral of flipflop is

begin

dff_1: process (clock, reset)

begin

if (reset = '0') then

q <= '0';

elsif (clock'event and clock = '1') then

q <= data;

end if;

end process dff_1;

end behavioral;</pre>

```

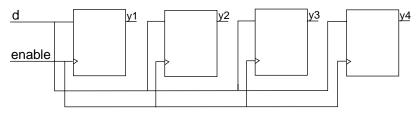

#### Inferring Latches

The following example, illustrated in Figure 2-10, infers a multi-bit D latch with an active high enable and an active low asynchronous clear:

Figure 2-10. Multi-bit D Latch

```

architecture behavioral of latches is

begin

dlc_1: process (enable, reset, d)

```

```

begin

if (reset = '0') then

y <= "0000";

elsif (enable = '1') then

y <= d;

end if;

end process dlc_1;

end behavioral;</pre>

```

#### Incomplete Sensitivity Lists

Incomplete sensitivity lists in a process may cause differences in the pre and post synthesis behavior. The following example demonstrates the incorrect way to synthesize a three-input AND gate, because the signal "c" is not in the sensitivity list. Therefore, the variable "y" is not re-evaluated when c changes.

```

architecture behavioral of tand3 is

begin

and3_1: process (a, b)

begin

if (reset = '0') then

y <= a and b and c;

end process and3_1;

end behavioral;</pre>

```

The correct method to synthesize a three-input and gate is as follows:

```

architecture behavioral of tand3 is

begin

and3_1: process (a, b, c)

begin

if (reset = '0') then

y <= a and b and c;

end process and3_1;

end behavioral;</pre>

```

Note: ACTmap does not always correctly report missing signals in the sensitivity list of a process. To avoid erroneous results during simulation, make sure that all sensitivity lists do not have missing signals.

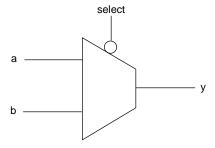

#### Incomplete Construct Value Specification

The if then else and case statements can infer latches instead of multiplexers if all possible states or values are not specified. The following example, illustrated in Figure 2-11, infers a 2 to 1 multiplexer:

Figure 2-11. 2 to 1 Multiplexer

```

if (select = '0') then

y <=a;

else

y <= b;

end if;</pre>

```

If you do not specify the else statement, a latch, illustrated in Figure 2-12, is inferred:

Figure 2-12. Latch Diagram

```

if (select) then

y <= a;

end if;</pre>

```

## State Machine Design

A state machine is a sequencer that is organized as a finite set of states. Each state represents one set of actions, such as enabling a counter to increment or generating an acknowledge output. Almost all states also contain a method of transferring control to another state based on certain conditions. Any state that does not have a means of going to another state would have to be the last state of the state machine, and the system would remain in this state forever. Transferring between states can be conditional (based on the values of other signals in the system) or non-conditional.

There are many ways to describe a finite state machine (FSM) in VHDL. The important point is that the synthesis tool should optimize the corresponding logic in an efficient way for both speed and area. This is done by applying optimized automatic state assignments. This section describes three types of FSM, the single-process, the double process, and a user defined FSM.

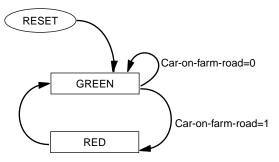

#### Single Process FSM

Figure 2-13 illustrates a single-process FSM that controls a traffic light. The sensitivity list of the process contains only two signals: the clock and the reset signals. To describe the transitions between states, a case statement identifies which state is considered. In the case statement, all state register values have to be enumerated in when statements. The state registers may be assigned conditionally in an if statement or not. The conditions are boolean expressions of the input ports.

Figur@-13.

library ieee;

```

use ieee.std_logic_1164.all;

entity light is

port (

clock: in std_logic;

reset: in std_logic;

car_on_farm_road: in std_logic;

set_green_on_highway: out std_logic);

end tlight;

architecture state_machine of light is

type state_type is (red, green);

signal next_state: state_type;

begin

sequencer: process (reset, clock)

begin

if (reset = '0') then

next_state <= green;

set_green_on_highway <= '1';</pre>

elsif (clock'event and clock = '1') then

case next_state is

when green =>

set_green_on_highway <= '1';</pre>

if (car_on_farm_road = '1') then

next_state <= red;</pre>

else

next_state <= green;

end if;

when red =>

set_green_on_highway <= '0';

next_state <= green;

end case;

end if;

end process sequencer;

end state_machine;

```

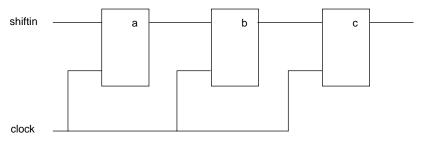

#### Double Process FSM

A common approach to describing an FSM uses two processes. One process defines registers or synchronization. The other process describes the combinatorial logic to define the next state and the outputs.

The first process sets the current state and the registered outputs of the FSM. This process is triggered by the clock and the reset signals. Therefore, it is executed when either signal changes. The FSM must be

triggered on the clock edge. You can trigger on either a rising or falling edge. It is not necessary to have a reset, but if a reset signal exists, it must be asynchronous. It may be active high or active low. The process should use the following template:

```

registers: process (clock, reset)

begin

if (reset = <'1','0'>) then

... reset the value of the state ...

... optionally reset the registered outputs ...

elsif (clock'event and clock = <'1','0'>) then

... Set the new FSM state ...

... Assign values to the registered outputs ...

end if;

end process registers;

```

Another process updates the present state with the next state and takes care of any combinatorial logic. The process is sensitive to all of the input signals and the signal that maintains the current state. It must also include all the internal signals that affect the output of the process. A case statement typically calculates the next state and the outputs as in the following template:

```

transitions : process (clock, reset)

begin

... Assign default values to all unregistered outputs ...

case present_state is

when state_0 =>

output <= <value>;

next_state <= <value>;

when state_1 => ...;

.

.

.

when others => ...;

end case;

end process registers;

```

Note: A value must be assigned to all unregistered outputs for each state. If you do not assign output values, the FSM maintains the previous values and creates unnecessary latches during synthesis. To avoid this problem, assign a default value to all unregistered outputs at the beginning of this process before the case

statement. Default assignments of an if statement within a case statement must be declared explicitly.

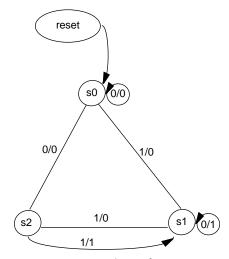

The following is an example of a simple Mealy FSM using two processes. Figure 2-14 and Table 2-2 illustrate the example:

Figure 2-14. Mealy FSM

Table 2-2. Mealy FSM State Table

| Present<br>State | Next State |     | Output |     |

|------------------|------------|-----|--------|-----|

|                  | x=0        | x=1 | x=0    | x=1 |

| s0               | s0         | s1  | 0      | 0   |

| s1               | s1         | s2  | 1      | 0   |

| s2               | s0         | s1  | 0      | 1   |

library ieee;

use ieee.std\_logic\_1164.all;

```

entity mealy is

port (

a: in std_logic;

clock: in std_logic;

reset: in std_logic;

z: out std_logic);

end mealy;

architecture state_machine of mealy is

type state_type is (s0, s1, s2);

signal current_state, next_state: state_type;

begin

registers: process (reset, clock)

begin

if (reset = '0') then

current_state <= s0;</pre>

else

if (clock'event and clock = '1') then

current_state <= next_state;</pre>

end if;

end if;

end process registers;

combinatorial: process (current_state)

begin

case current_state is

when s0 =>

if (a = '0') then

z <= '0';

next_state <= s0;</pre>

else

z <= '0';

next_state <= s1;</pre>

end if;

when s1 =>

if (a = '0') then

z <= '1';

next_state <= s1;

else

z <= '0';

next state <= s2;

end if;

when s2 =>

if (a = '0') then

z <= '0';

next_state <= s0;</pre>

else

z <= '1';

```

```

next_state <= s1;

end if;

end case;

end process combinatorial;

end state_machine;</pre>

```

#### User Defined FSM

An FSM can also be defined to your specification. Each state is defined as a constant with a unique value. Below is an example of a counter defined as an FSM using user-defined states:

```

entity count4c is

port (

reset: in bit;

clock: in bit;

s : out bit_vector(3 downto 0);

load data : in bit vector(3 downto 0);

load : in bit;

enable : in bit);

end count4c;

architecture state_machine of count4c is

signal state, next_state: bit_vector(3 downto 0);

-- usually this can be an integer

constant state0: bit_vector ( 3 downto 0) := "1111";

constant state1: bit_vector ( 3 downto 0) := "1110";

constant state2: bit_vector ( 3 downto 0) := "1101";

constant state3: bit_vector ( 3 downto 0) := "1100";

constant state4: bit_vector ( 3 downto 0) := "1011";

constant state5: bit_vector ( 3 downto 0) := "1010";

constant state6: bit_vector ( 3 downto 0) := "1001";

constant state7: bit_vector ( 3 downto 0) := "1000";

constant state8: bit_vector ( 3 downto 0) := "0111";

constant state9: bit_vector ( 3 downto 0) := "0110";

constant statea: bit_vector ( 3 downto 0) := "0101";

constant stateb: bit_vector ( 3 downto 0) := "0100";

constant statec: bit_vector ( 3 downto 0) := "0011";

constant stated: bit_vector ( 3 downto 0) := "0010";

constant statee: bit_vector ( 3 downto 0) := "0001";

constant statef: bit_vector ( 3 downto 0) := "0000";

begin

sequential: process (clock, reset)

begin

if (reset = '1') then

state <= state0;</pre>

elsif (clock'event and clock = '1') then

```

```

if ( load = '1' ) then

state <= load_data;</pre>

elsif ( enable = '1' ) then

state <= next_state;</pre>

else

state <= state;

end if;

end if;

end process sequential;

combinatorial: process (state)

begin

case state is

when state0 =>

next_state <= state1;</pre>

s <= x"0";

when state1 =>

next_state <= state2;</pre>

s <= x"1";

when state2 =>

next_state <= state3;</pre>

s <= x"2";

when state3 =>

next_state <= state4;</pre>

s <= x"3";

when state4 =>

next_state <= state5;</pre>

s <= x"4";

when state5 =>

next_state <= state6;</pre>

s <= x"5";

when state6 =>

next_state <= state7;</pre>

s <= x"6";

when state7 =>

next_state <= state8;</pre>

s <= x"7";

when state8 =>

next_state <= state9;</pre>

s <= x"8";

when state9 =>

next_state <= statea;

s <= x"9";

when statea =>

next_state <= stateb;

s <= x"a";

when stateb =>

next_state <= statec;</pre>

```

```

s <= x"b";

when statec =>

next_state <= stated;

s <= x"c";

when stated =>

next_state <= statee;

s <= x"d";

when statee =>

next_state <= statef;

s <= x"e";

when statef =>

next_state <= state0;</pre>

s <= x"f";

when others => null;

end case;

end process combinatorial;

end state machine;

```

## Supported Packages

There are a number of operations in VHDL that occur regularly. An example is translation of vectors to integers and back. For this reason, ACTmap provides packages that define attributes, functions and procedures that are often used. Using the functions and procedures reduces the amount of initial circuitry that is generated, compared to writing the behavior explicitly in a user-defined function or procedure. This reduces the time for compilation and also could result in a smaller circuit implementation due to improved optimization.

#### Actel Component Packages

Users instantiating Actel macros in their designs do not need to declare the Actel components. ACTmap maintains a compiled version of the component. The VHDL source for these packages is located in the "<actel\_install\_directory>/lib/actel/vhdl/<act\_fam>" directory. The macro component declarations are included by using the following use statement:

```

library <act_fam>;

use <act_fam>.components.all;

```

Note: The component package for the Actel family being targeted should be compiled before the VHDL code referencing the components.

#### **IEEE Packages**

ACTmap supports the following IEEE packages:

- std\_logic\_1164

- std\_logic\_unsigned

- std\_logic\_arith

The textio package is not supported.

## **Using Procedures**

This section lists guidelines to follow when using procedures in ACTmap.

#### Intermediate Signals

When using procedures, ACTmap requires the use of intermediate signals.

The following example does not work:

```

user_procedure(conv_integer(aaa));

```

The procedure should be written as follows:

```

int_aaa <= conv_integer(aaa);

user_procedure(int_aaa);</pre>

```

#### Inout Parameters Not Supported

ACTmap does not support the use of inout parameters for procedures. The parameters must be either in or out. ACTmap displays the following error message if a procedure has an inout parameter:

```

ERROR: (VHDL_1768). Line 88. Inout parameter not yet supported.

```

#### Limitations

This section lists known limitations and unsupported features in ACTmap VHDL.

#### Bi-Directional Buffers

When using bi-directional buffers, make sure the feedback signal connects to internal logic. If the feedback signal is not connected to internal logic, ACTmap connects the BIBUF macro incorrectly.

#### Preserving Character Case

The "AMP\_EDIFUPPER" environment variable, which forces all characters to upper case, is set to "YES" in ACTmap. If you want ACTmap to preserve character case in your VHDL code, you must set the "AMP\_EDIFUPPER" environment variable to no.

#### **Event Construct**

ACTmap does not support the event construct for a vector bit. The following example produces an error:

```

architecture behavioral of bug is

signal vector : std_logic_vector( 7 downto 0);

begin

process (vector)

begin

if (vector(0)'event )then

k <= jj;

else

k(6 downto 0) <= jj and vector(6 downto 0);

k(7) <= 'l';

end if

end process;

end behavioral;</pre>

```

The above example should be written as follows:

```

architecture behavioral of bug is

signal vector : std_logic_vector( 7 downto 0);

signal e_vector: std_logic; -this line is added

begin

e_vector <= vector(0); -this line is added

process (e_vector, vector) -this line is changed

begin</pre>

```

```

if (e_vector'event )then -this line is changed

k <= jj;

else

k(6 downto 0) <= jj and vector(6 downto 0);

k(7) <= '1';

end if

end process;

end behavioral;</pre>

```

#### Multiple Clock Events

Multiple clock events are not supported. The following examples do not work:

```

if (rst'event and rst = '0') then

...

elsif (clk'event and clk = '1') then

...

end if;

if ((rst'event and rst = '0') and (clk'event and clk = '1'))

then

...

end if;

```

#### VHDL 92 and 93

The set of constructs added in the VHDL 92 and 93 specification were intended to be used for simulation purposes and are not supported in ACTmap.

#### **Bus Width Errors**

ACTmap does not always correctly report bus width errors. Make sure that all of your bus widths match in your VHDL code or ACTmap may produce erroneous results.

#### Multi-Dimensional Buses

ACTmap does not support multi-dimensional buses.

#### Chapter 2: Using ACTmap VHDL

#### Unsupported Data Types

The following data types are not supported: physical, floating point, signed arrays, access, and file. User defined arrays are only supported for a dimension not exceeding 2.

#### Wait For Time Construct

The "wait for time" construct is not supported.

#### Loop Statements

The "while...loop... end loop" and the "loop...end loop" statements are not supported.

#### Indexed and Sliced Signals in Sensitivity List

ACTmap does not support the use of indexed or sliced signals in the sensitivity list of a process.

The following example is not supported:

```

process ( a(7), b(6 downto 4), s3)

```

The above example should be written as follows:

```

int_a <= a(7);

int_b <= b(6 downto 4);

...

process (int_a, int_b)</pre>

```

#### Object Specification Must Be a Constant

The following construct is not supported by ACTmap VHDL:

```

process

begin

wait until clk'event and clk = '1';

b_r <= (others => '0');

a_r <= (others => b_r);

end process;

```

The above example should be written as follows:

```

process

begin

wait until clk'event and clk = '1';

a_r <= (others => (others => '0'));

end process;

```

## **Advanced Optimization Techniques**

This chapter describes optimization guidelines and features in ACTmap. This includes ACTmap VHDL and general optimization guidelines, information about optimizing state machines, and using design constraints during optimization. Also included is information about the ACTmap automatic I/O insertion and sequential remapping features, and information about using special cells in 3200DX and 42MX devices to improve performance. Finally, information about gated macro usage and about where to find radiation environment design techniques is given.

## **ACTmap VHDL Guidelines**

The following are ACTmap VHDL guidelines to assist you in obtaining the best synthesis results possible:

- For the ACT 3 FPGA family devices, Actel recommends that you avoid describing reset and clear flips-flops and latches in your VHDL descriptions. The ACT 3 preset and clear flip-flops cannot be connected to the hardwired global clock networks driven by HCLKBUF. For ACT 2 and ACT 3 family devices, use asynchronous clear latches and flip-flops. The active low asynchronous clear flip-flops and latches are ACTmap's basic building blocks. Using them may result in better optimization.

- Actel recommends that you avoid describing any flips flops and latch

configurations that do not have an asynchronous clear input. The JK

or toggle flip-flops, without any asynchronous clear or preset (with

sequential remapping) feature may not be simulated by your CAE

simulator tools.

## General Optimization Guidelines

One of the most powerful features of the ACTmap program is its optimization capability. The optimization and mapping technique used in ACTmap is designed to improve the area or speed of most designs targeted for Actel devices. However, this does not mean that the algorithm can improve all designs. This section lists guidelines to keep in mind when optimizing your design with ACTmap.

#### Chapter 3: Advanced Optimization Techniques

#### Logic Design Type

The type of logic used in the design affects how much of the design can be optimized. ACTmap's algorithm produces excellent results when optimizing random logic, but it does not work as well for structured logic blocks such as adders, subtractors, comparators, and accumulators. Many counters, adders, subtractors, decoders and multiplexers can be inferred through VHDL descriptions or generated using the ACTgen Macro Builder. Other logic blocks can also be created by the ACTgen Macro Builder and added to a design. Refer to "Inferring ACTgen Macros" on page 24" and "ACTgen Macros" on page 21 for information about integrating an ACTgen macro into your design.

#### Design Optimization Level

You must consider whether to optimize the complete design, or only a part of the design (generally, Actel recommends that you use smaller blocks for better optimization). At times it is beneficial to optimize the whole chip because chip optimization can break down the boundaries between the functional blocks. This allows ACTmap to globally consider the logic that is optimized, which often produces better results.

Note: ACTmap may not produce improved results when optimizing highly structured or optimized designs.

#### Limited Optimization

If you are using an original design that has only structured or optimized sections, you can instruct ACTmap to ignore the optimal sections.