# In-System Programmability

in MAX Devices

August 1999, ver. 1.02

Application Note 95

# Introduction

MAX<sup>®</sup> devices are programmable logic devices (PLDs), based on the Altera<sup>®</sup> Multiple Array MatriX (MAX) architecture that and supports the IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface. MAX devices are also in-system programmable, which adds programming flexibility and provides benefits in many phases of product development, manufacturing, and field use. This application note provides background information on in-system programmability (ISP) and the IEEE Std. 1149.1 JTAG interface and discusses the advantages of using ISP-capable MAX devices.

# Features & Benefits

In-system design, prototyping, and manufacturing, reduces cost, shortens development time, and provides a wider range of programming options than standard device programming methods. With ISP, you can:

- Program and reprogram devices after they are soldered onto the printed circuit board (PCB), minimizing the possibility of lead damage or electrostatic discharge (ESD) exposure.

- Manufacture systems before you finalize device configuration.

- Perform boundary-scan test (BST) procedures and program devices using in-circuit testers.

- Upgrade systems in the field after they have been shipped.

Table 1 describes the features and benefits of using ISP-capable MAX devices.

| Product Development<br>Phase | Features                                                                                                                                                                                                           | Benefits                                                                                                                                                               |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device prototyping           | Devices are programmed with a V <sub>CC</sub> -level programming voltage.                                                                                                                                          | Eliminates the need for a 12.0-V<br>programming voltage and the possibility of<br>accidental damage to lower voltage parts.<br>Also reduces system power requirements. |

|                              | Devices can be programmed while soldered to a PCB.                                                                                                                                                                 | Minimizes device handling, thereby<br>protecting devices from ESD and lead<br>damage.                                                                                  |

|                              | Prototype systems can be assembled<br>before the device configuration is<br>finalized.                                                                                                                             | Cuts prototype development time and saves development costs.                                                                                                           |

| System manufacturing         | PLDs can be treated the same way as<br>other board-level devices because they<br>can be programmed after the PCB is<br>assembled.                                                                                  | Simplifies manufacturing, saves time, and protects devices from ESD and lead damage.                                                                                   |

|                              | ISP is implemented using the IEEE Std.<br>1149.1 (JTAG) interface; therefore, circuit<br>testing and device programming can be<br>combined into a single manufacturing step<br>using a standard in-circuit tester. |                                                                                                                                                                        |

|                              | Programming data can be downloaded<br>from in-circuit testers, PCs, or<br>workstations during final PCB test.                                                                                                      |                                                                                                                                                                        |

|                              | Devices can be programmed with test configurations.                                                                                                                                                                | Enhances design debugging and board-<br>level testing capabilities.                                                                                                    |

| In-field programming         | Devices can be reprogrammed in the field.                                                                                                                                                                          | Adds versatility and reduces service costs,<br>thereby making products more attractive to<br>the consumer.                                                             |

# V<sub>CC</sub>-Level Programming

ISP-capable MAX devices support ISP through a  $V_{CC}$ -level programming voltage. The devices generate a 12.0-V programming voltage internally to program, verify, and erase the device's EEPROM cells, eliminating the need for the external 12.0-V programming voltage typically required for programming.

ISP-capable MAX devices are guaranteed for 100 erase and programming cycles with 100% programming and functional yields.

# Programming Systems

In Altera devices, ISP is implemented using the IEEE Std.1149.1 JTAG interface, which streamlines PCB testing and device programming operations into a single manufacturing step.

ISP-capable MAX devices are supported by the following systems:

- MAX+PLUS II development system

- In-circuit testers

- Embedded processors

### MAX+PLUS II Development System

You can use a PC or UNIX workstation, the MAX+PLUS II Programmer, and the BitBlaster<sup>™</sup> serial or ByteBlasterMV<sup>™</sup> parallel port download cable to download Programmer Object Files (**.pof**), Jam Files (**.jam**), or Jam<sup>™</sup> Byte-Code Files (**.jbc**)from the MAX+PLUS II software to ISPcapable MAX devices mounted on a PCB. This method is more costeffective than other programming methods because design, simulation, and prototyping can be performed using the same PC- or UNIX workstation-based system.

For production, you can implement ISP using Altera's free stand-alone programming software and the BitBlasterMV cable to download POFs.

PC-based stand-alone programming software, asap2.exe, is available from Altera's FTP site at ftp.altera.com in the \pub\misc directory.

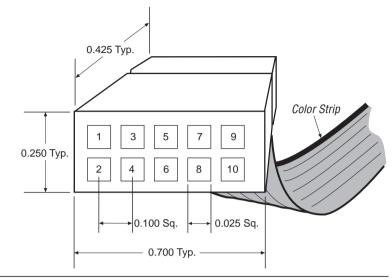

Figure 1 shows the 10-pin female plug dimensions for the BitBlaster or ByteBlaster download cable.

#### Figure 1. 10-Pin Female Plug Dimensions

Dimensions are shown in inches. The spacing between pin centers is 0.1 inch.

Table 2 identifies the 10-pin female plug's pin names for the corresponding download mode.

| Table 2. Female Plug's Pin Names & Download Modes |             |                               |             |                       |  |  |  |

|---------------------------------------------------|-------------|-------------------------------|-------------|-----------------------|--|--|--|

| Pin                                               | JTAG Mode   |                               | PS Mode     |                       |  |  |  |

|                                                   | Signal Name | Description                   | Signal Name | Description           |  |  |  |

| 1                                                 | TCK         | Clock signal                  | DCLK        | Clock signal          |  |  |  |

| 2                                                 | GND         | Signal ground                 | GND         | Signal ground         |  |  |  |

| 3                                                 | TDO         | Data from device              | CONFIG_DONE | Configuration control |  |  |  |

| 4                                                 | VCC         | Power supply                  | VCC         | Power supply          |  |  |  |

| 5                                                 | TMS         | JTAG state<br>machine control | nCONFIG     | Configuration control |  |  |  |

| 6                                                 | _           | No connect                    | _           | No connect            |  |  |  |

| 7                                                 | _           | No connect                    | nSTATUS     | Configuration status  |  |  |  |

| 8                                                 | _           | No connect                    | _           | No connect            |  |  |  |

| 9                                                 | TDI         | Data to device                | DATA0       | Data to device        |  |  |  |

| 10                                                | GND         | Signal ground                 | GND         | Signal ground         |  |  |  |

P

The circuit board must supply  $V_{CC}$  and ground to the ByteBlaster cable.

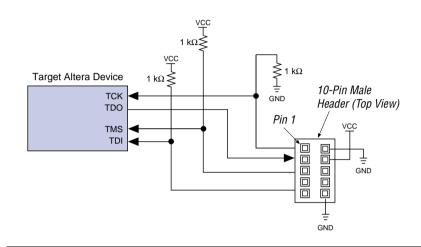

ISP-capable devices are programmed via a device's JTAG pins: TCK, TMS, TDI, and TDO. Figure 2 shows how the BitBlaster or ByteBlaster download cable interfaces with an ISP-capable device. The I/O pins are tri-stated during in-system programming.

Search for "Programming a Single Device with the BitBlaster or ByteBlaster" in MAX+PLUS II Help, or go to the *BitBlaster Serial Download Cable Data Sheet* and *ByteBlaster Parallel Port Download Cable Data Sheet* in this handbook for more information.

### **In-Circuit Test Programming**

You can program ISP-capable MAX devices during the final PCB testing stage using in-circuit testers and the IEEE Std. 1149.1 (JTAG) interface. To program a device using in-circuit testers, create a Jam or SUF File with the MAX+PLUS II software and download this file from an in-circuit test station to one or more ISP-capable MAX devices.

Go to *Product Information Bulletin 27 (Jam Programming and Test Language Overview)* and the *Jam Programming and Test Language Specification*, version 1.1 in this handbook for more information on Jam Files.

### **Embedded Processor Programming**

You can program ISP-capable MAX devices in-system using an embedded processor. For example, programming information can be stored in an EPROM and shifted into the ISP-capable MAX device using a 4-bit interface from the processor to the device's JTAG pins. This method lets you program devices during burn-in and upgrade devices in the field.

You can program MAX devices with an embedded processor by creating a Jam File from the MAX+PLUS II software and downloading it with the Jam Player.

IEEE Std.

1149.1 Interface Go to Application Note 88 (Using the Jam Language for ISP & ICR via an Embedded Processor) for more information on embedded processor programming. Go to Product Information Bulletin 27 (Jam Programming and Test Language Overview) and the Jam Programming and Test Language Specification, version 1.1 in this handbook for more information on the Jam Player.

MAX device JTAG pins and functions are described in Table 3.

| Pin | Description      | Function                                                                                                                                                                                |  |

|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TDI | Test data input  | Serial input pin for data and instructions, which are shifted in on the rising edge of TCK. This signal needs to be externally pulled high during normal operation.                     |  |

| TDO | Test data output | Serial data output pin for instructions and data. Data is shifted out on the falling edge of TCK. This signal is tri-stated if data is not being shifted out of the device.             |  |

| TMS | Test mode select | Input pin controls the IEEE Std. 1149.1 JTAG state<br>machine and is evaluated on the rising edge of TCK.<br>This signal needs to be externally pulled high during<br>normal operation. |  |

| TCK | Test clock       | Provides the clock signal for the JTAG circuits. The maximum operating frequency is 10 MHz. This signal needs to be externally pulled low during normal operation.                      |  |

#### Table 3. JTAG Pins

During erasure, programming, and verification, all device I/O pins are tri-stated to eliminate interference from other devices on the PCB. Devices are programmed by applying the appropriate signals on the TMS and TCK inputs and shifting data into and out of the devices on the TDI and TDO pins, respectively. After programming, the IEEE Std. 1149.1 JTAG Test Access Port (TAP) controller state machine must be advanced to the RESET state, which is maintained by external pull-up resistors on the TCK, TMS, and TDI pins. During normal operation, the pull-up resistors prevent the device from entering other modes.

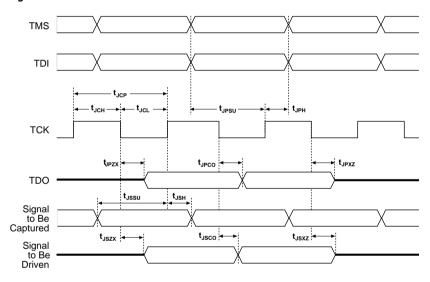

Figure 3 shows the timing waveforms for the IEEE Std. 1149.1 JTAG TAP controller state machine.

Table 4 shows the JTAG timing parameters and values for ISP-capable MAX devices.

| Table 4. JTAG Timing Parameters & Values for MAX Devices |                                                |     |     |      |  |  |

|----------------------------------------------------------|------------------------------------------------|-----|-----|------|--|--|

| Symbol                                                   | Parameter                                      | Min | Max | Unit |  |  |

| t <sub>JCP</sub>                                         | TCK clock period                               | 100 |     | ns   |  |  |

| t <sub>JCH</sub>                                         | TCK clock high time                            | 50  |     | ns   |  |  |

| t <sub>JCL</sub>                                         | TCK clock low time                             | 50  |     | ns   |  |  |

| t <sub>JPSU</sub>                                        | JTAG port setup time                           | 20  |     | ns   |  |  |

| t <sub>JPH</sub>                                         | JTAG port hold time                            | 45  |     | ns   |  |  |

| t <sub>JPCO</sub>                                        | JTAG port clock to output                      |     | 25  | ns   |  |  |

| t <sub>JPZX</sub>                                        | JTAG port high impedance to valid output       |     | 25  | ns   |  |  |

| t <sub>JPXZ</sub>                                        | JTAG port valid output to high impedance       |     | 25  | ns   |  |  |

| t <sub>JSSU</sub>                                        | Capture register setup time                    | 20  |     | ns   |  |  |

| t <sub>JSH</sub>                                         | Capture register hold time                     | 45  |     | ns   |  |  |

| t <sub>JSCO</sub>                                        | Update register clock to output                |     | 25  | ns   |  |  |

| t <sub>JSZX</sub>                                        | Update register high impedance to valid output |     | 25  | ns   |  |  |

| t <sub>JSXZ</sub>                                        | Update register valid output to high impedance |     | 25  | ns   |  |  |

- --- 4 ITAO Timir \_ 0 1/-1

Go to Application Note 39 (IEEE Std.1149.1 (JTAG) Boundary-Scan Testing in Altera Devices) for information on the IEEE Std.1149.1 JTAG TAP controller state machine.

# Programming **ISP-Capable MAX** Devices

You can use an IEEE Std.1149.1 JTAG-compatible header to program a single device or a chain of devices, depending on the layout of your PCB.

### **Single-Device Programming**

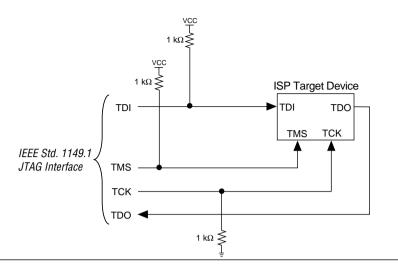

For PCBs that contain a single ISP-capable MAX device, a JTAG-compatible header—such as the 10-pin BitBlaster or ByteBlaster header—can be used to program the device. See Figure 4.

### JTAG-Chain Device Programming

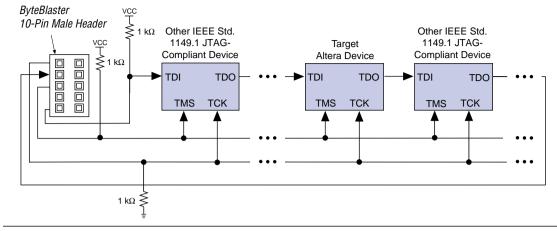

When programming a chain of devices, one JTAG-compatible plug, such as a BitBlaster or ByteBlaster 10-pin male plug, is connected to several devices. The number of devices in the JTAG chain is limited only by the drive capability of the BitBlaster or ByteBlaster download cable. However, when three or more devices are connected in a JTAG chain, Altera recommends buffering the TDO, TCK, TDI, and TMS pins.

JTAG-chain device programming is ideal when the circuit board contains multiple devices, or when the circuit board is tested using JTAG BST. See Figure 5.

#### Figure 5. JTAG-Chain Device Programming with a BitBlaster or ByteBlaster Cable

To program a single ISP-capable MAX device in a JTAG chain, the programming software puts all other devices in the JTAG chain in BYPASS mode. When in BYPASS mode, devices pass programming data from the TDI pin to the TDO pin through a single bypass register. Bypassed devices are not affected internally, thereby enabling the programming software to erase, program, or verify the target device.

Go to *Application Note 39* (IEEE 1149.1 (JTAG) Boundary-Scan Testing in *Altera Devices*) for more information on the BYPASS mode.

## Conclusion

ISP-capable MAX devices offer benefits in product design, prototyping, and manufacturing. ISP simplifies the manufacturing flow by allowing the devices to be mounted on a PCB with standard pick-and-place equipment before they are programmed. ISP-capable MAX devices can be programmed by downloading the information via in-circuit testers, embedded processors, or the BitBlaster or ByteBlaster download cables. In addition, programming these devices after they are placed on the board eliminates lead damage on high pin-count packages, e.g., quad flat pack (QFP) packages, due to device handling. These devices can also be reprogrammed in the field (i.e., product upgrades can be performed in the field via software or modem).

# Revision History

The information contained in Application Note 95 (In-System Programmability in MAX Devices) version 1.02 supersedes information published in previous versions.

### Version 1.02 Changes

Application Note 95 (In-System Programmability in MAX Devices) version 1.02 contains the following changes:

- Corrected TCK information in Table 2.

- Corrected Figure 2.

### Version 1.01 Changes

Application Note 95 (In-System Programmability in MAX Devices) version 1.01 contained the following changes:

- Corrected information on the number of devices connected in a JTAG chain in "JTAG-Chain Device Programming" on page 9.

- Made minor illustrative, textual, and style changes.

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com **Applications Hotline:** (800) 800-EPLD **Customer Marketing:** (408) 544-7104 Literature Services: (408) 544-7144 lit\_reg@altera.com

Altera, MAX, MAX+PLUS, MAX+PLUS II, FLEX, FLEX 10K, FLEX 10KA, FLEX 8000, FLEX 8000A, FLEX 6000, MAX 9000, MAX 9000A, MAX 7000, MAX 7000S, MAX 7000A, EPF10K10, EPF10K10A, EPF10K20, EPF10K30, EPF10K30A, EPF10K40, EPF10K50, EPF10K50V, EPF10K70, EPF10K100, EPF10K100A, EPF8282A, EPF8282AV, EPF8820A, EPM9320, EPM9320A, EPM9400, EPM9480, EPM9480A, EPM9560, EPM9560A, EPM7032S, EPM7064S, EPM7064A, EPM7128S, EPM7128A, EPM7160S, EPM7192S, EPM7256S, EPM7256A, EPM7384A, EPM7512A, and EPM71024A are trademarks and/or service service marks of Altera Corporation in the United States and other countries. Altera acknowledges the trademarks of other organizations for their respective products or services mentioned in this document. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice.

Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Copyright © 1999 Altera Corporation. All rights reserved.

**I.S. EN ISO 9001**

**Altera Corporation**

11