# Foundation Series ISE 3.1i Quick Start Guide

Introduction Setting Up the Tools Software Overview Basic Tutorial

Glossary

Foundation Series ISE 3.1i Quick Start Guide

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

ASYL, FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CoolRunner, CORE Generator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Fast Zero Power, Foundation, HardWire, IRL, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, MultiLINX, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebFitter, WebLINX, WebPACK, XABEL, XACT*step*, XACT*step* Advanced, XACT*step* Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4.642.487: 4.695.740: 4.706.216: 4.713.557: 4.746.822: 4.750.155: 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5.737.631: 5.742.178: 5.742.531: 5.744.974: 5.744.979: 5.744.995: 5.748.942: 5.748.979: 5.752.006: 5.752.035: 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; 5,861,761; 5,862,082; 5,867,396; 5,870,309; 5,870,327; 5,870,586; 5,874,834; 5,875,111; 5,877,632; 5,877,979; 5,880,492; 5,880,598; 5,880,620; 5,883,525; 5,886,538; 5,889,411; 5,889,413; 5,889,701; 5,892,681; 5,892,961; 5,894,420; 5,896,047; 5,896,329; 5,898,319; 5,898,320; 5,898,602; 5,898,618; 5,898,893; 5,907,245; 5,907,248; 5,909,125; 5,909,453; 5,910,732; 5,912,937; 5,914,514; 5,914,616; 5,920,201; 5,920,202; 5,920,223; 5,923,185; 5,923,602; 5,923,614; 5,928,338; 5,931,962; 5,933,023; 5,933,025; 5,933,369; 5,936,415; 5,936,424; 5,939,930; 5,942,913; 5,944,813; 5,945,837; 5,946,478; 5,949,690; 5,949,712; 5,949,983; 5,949,987; 5,952,839; 5,952,846; 5,955,888; 5,956,748; 5,958,026; 5,959,821; 5,959,881; 5,959,885; 5,961,576; 5,962,881; 5,963,048; 5,963,050; 5,969,539; 5,969,543; 5,970,142; 5,970,372; 5,971,595; 5,973,506; 5,978,260; 5,986,958; 5,990,704; 5,991,523; 5,991,788; 5,991,880; 5,991,908; 5,995,419; 5,995,744; 5,995,988; 5,999,014; 5,999,025; 6,002,282; and 6,002,991; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-2000 Xilinx, Inc. All Rights Reserved.

## **About This Manual**

This guide should be used as the initial learning tool for designers who are unfamiliar with the features of the Foundation Series Integrated Synthesis Environment (ISE) 3.1i software.

Note This Xilinx software release is certified as Year 2000 compliant.

### **Manual Contents**

This guide covers the following topics.

- Chapter 1, "Introduction" describes the key features of the ISE software and lists available documentation.

- Chapter 2, "Setting Up the Tools," gives instructions for installing the ISE software and provides you with information about the type of computer you need to successfully implement your designs.

- Chapter 3, "Software Overview," describes the capability and flexibility of the ISE software.

- Chapter 4, "Basic Tutorial" provides a step-by-step example explaining how to use the basic ISE tools.

- The "Glossary," defines some of the commonly used terms in this Guide.

## **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this Web site. You can also directly access these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                                                                                                                          |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Tutorials            | Tutorials covering Xilinx design flows, from design entry to verification<br>and debugging<br>http://support.xilinx.com/support/techsup/tutorials/<br>index.htm                                                                                                          |  |

| Answers<br>Database  | Current listing of solution records for the Xilinx software tools<br>Search this database using the search function at<br>http://support.xilinx.com/support/searchtd.htm                                                                                                 |  |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches<br>http://support.xilinx.com/apps/appsweb.htm                                                                                                                                                           |  |

| Data Book            | Pages from <i>The Programmable Logic Data Book</i> , which contain device-<br>specific information on Xilinx device characteristics, including readback,<br>boundary scan, configuration, length count, and debugging<br>http://support.xilinx.com/partinfo/databook.htm |  |

| Xcell Journals       | Quarterly journals for Xilinx programmable logic users<br>http://support.xilinx.com/xcell/xcell.htm                                                                                                                                                                      |  |

| Technical Tips       | Latest news, design tips, and patch information for the Xilinx design<br>environment<br>http://support.xilinx.com/support/techsup/journals/<br>index.htm                                                                                                                 |  |

## Conventions

This manual uses the following conventions. An example illustrates each convention.

### Typographical

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

speed grade: - 100

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

rpt\_del\_net=

**Courier bold** also indicates commands that you select from a menu.

File  $\rightarrow$  Open

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

edif2ngd design\_name

References to other manuals

See the *Development System Reference Guide* for more information.

• Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

• Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on|off}

```

• A vertical bar " | " separates items in a list of choices.

lowpwr ={on|off}

• A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

.

```

• A horizontal ellipsis "...." indicates that an item can be repeated one or more times.

allow block block\_name loc1 loc2locn;

### **Online Document**

The following conventions are used for online documents.

• Red-underlined text indicates an interbook link, which is a cross-reference to another book. Click the red-underlined text to open the specified cross-reference.

• Blue-underlined text indicates an intrabook link, which is a cross-reference within a book. Click the blue-underlined text to open the specified cross-reference.

## Contents

### **About This Manual**

| Manual Contents      | . <b>i</b> |

|----------------------|------------|

| Additional Resources | ii         |

### Conventions

| Typographical   | iii |

|-----------------|-----|

| Online Document | iv  |

### Chapter 1 Introduction

| Key Features         | . 1-1 |

|----------------------|-------|

| Architecture Support |       |

| Documentation        | 1-3   |

### Chapter 2 Setting Up the Tools

| Product Configurations 2                                        | 2-1        |

|-----------------------------------------------------------------|------------|

| Installing Software 2                                           | 2-2        |

| Installing Xilinx Software 2                                    | 2-2        |

| Installing Documentation 2                                      | 2-3        |

| Installing Test Bench, Simulation, and State Machine Software 2 | 2-3        |

| Installing MXE Software 2                                       | <u>2-4</u> |

| Installing HDL Bencher and StateCAD Software                    | 2-4        |

| Special StateCAD/HDL Bencher Upgrade for Xilinx Users . 2       | 2-6        |

| Using Other Versions of ModelSim, HDL Bencher,                  |            |

| and StateCAD 2                                                  | 2-6        |

| Customer Service 2                                              | 2-7        |

| Technical Support 2                                             | 2-8        |

### Chapter 3 Software Overview

| Starting the Foundation Series ISE Software        |        |

|----------------------------------------------------|--------|

| Project Navigator                                  | . 3-2  |

| Project Navigator Online Help                      |        |

| Source Window                                      |        |

| Process Window                                     |        |

| Transcript Window                                  |        |

| Design Entry<br>HDL Editor                         |        |

| ECS Schematic Editor                               |        |

| Symbol Editor                                      |        |

| StateCAD and StateBench                            |        |

| LogiBLOX and CORE Generator Modules                |        |

| Design Synthesis                                   |        |

| XST                                                |        |

| FPGA Express                                       |        |

| Design Constraints                                 |        |

| Functional Simulation                              |        |

| Design Implementation                              |        |

| Interpreting the Reports                           |        |

| Translation Report                                 |        |

| Map Report (FPGAs)                                 |        |

| Pre-Route Static Timing Report (FPGAs Only)        |        |

| Place and Route Report (FPGAs)                     | . 3-14 |

| Pad Report (FPGAs)                                 |        |

| Asynchronous Delay Report (FPGAs)                  |        |

| Fitting Report (CPLDs)                             |        |

| Post Route Timing Report (FPGAs Only)              |        |

| Timing Report (CPLDs)                              |        |

| Lock Pins Report                                   |        |

| MPPR Report (FPGAs Only)                           |        |

| Other Design Implementation Tools                  |        |

| Floorplanner (FPGAs)                               |        |

| FPGA Editor                                        | . 3-17 |

| Post Fit ChipViewer (CPLDs)                        | . 3-18 |

| Timing Simulation                                  | . 3-18 |

| Device Programming                                 | . 3-18 |

| Create Programming File (FPGAs)                    | . 3-18 |

| Viewing Programming File Generation Report (FPGAs) |        |

| PROM File Formatter (FPGAs)                        |        |

| Hardware Debugger (FPGAs)                          | . 3-19 |

|                                                    |        |

|           | JTAG Programmer                                 | 3-19 |

|-----------|-------------------------------------------------|------|

| Chapter 4 | Basic Tutorial                                  |      |

|           | Introduction<br>Online Help                     |      |

|           | Hints                                           |      |

|           | Source and Process Windows                      |      |

|           | Schematic Editor Tips                           |      |

|           | General Object-Action vs. Action-Object         |      |

|           | Dragging a Net Name                             |      |

|           | Adding a Net Name to an I/O Wire                |      |

|           | Adding I/O Markers                              |      |

|           | Design Entry (VHDL)                             | 4-4  |

|           | Starting the ISE Software                       |      |

|           | Creating a New Project                          | 4-4  |

|           | Creating a 4-Bit Counter Module                 | 4-6  |

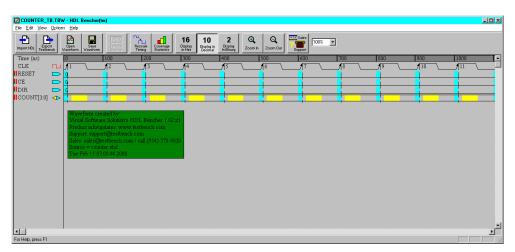

|           | Functional Simulation                           | 4-9  |

|           | Creating a Test Bench with HDL Bencher          | 4-9  |

|           | Adding the Test Bench File to the Project       | 4-12 |

|           | Simulating with ModelSim                        | 4-12 |

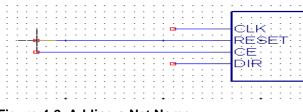

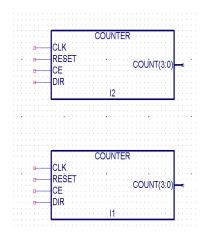

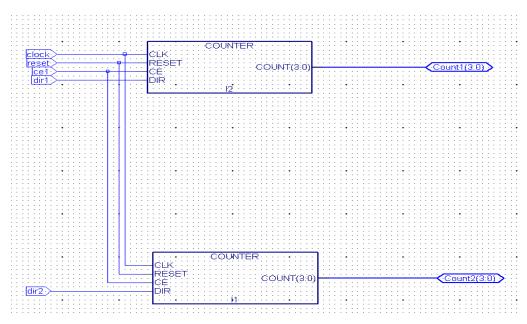

|           | Design Entry (Top-Level Schematic)              | 4-14 |

|           | Creating a Schematic Symbol for the VHDL Module | 4-14 |

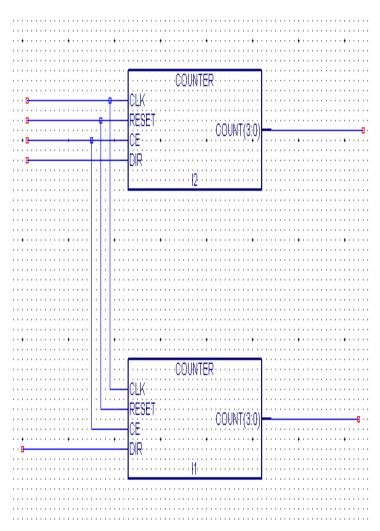

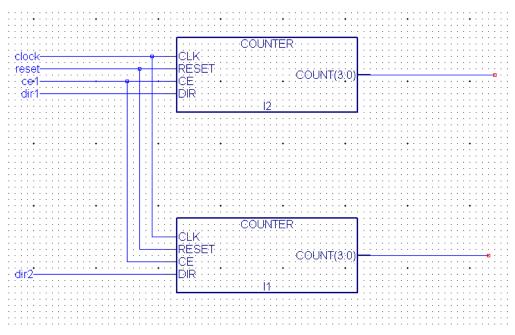

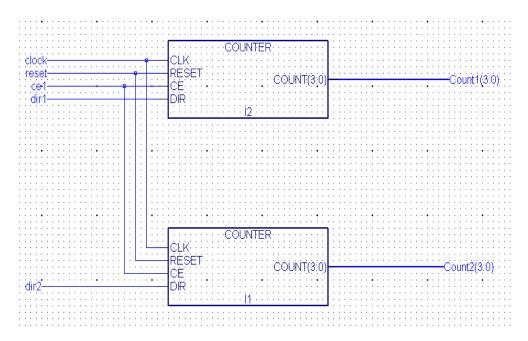

|           | Creating a New Top-Level Schematic              |      |

|           | Instantiating VHDL Modules                      | 4-15 |

|           | Wiring the Schematic                            |      |

|           | Adding Net Names to Wires                       | 4-18 |

|           | Creating Buses                                  |      |

|           | Adding I/O Markers                              |      |

|           | Design Implementation                           |      |

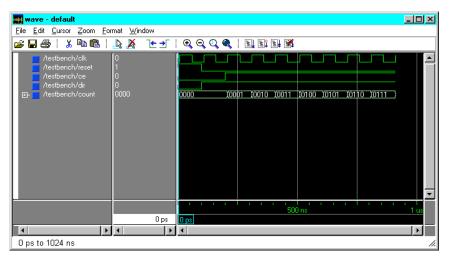

|           | Timing Simulation                               | 4-24 |

### Glossary

## **Chapter 1**

## Introduction

This Quick Start Guide explains how to install the software, describes the basic software tools, and provides a basic tutorial.

This chapter contains the following sections.

- "Key Features"

- "Architecture Support"

- "Documentation"

### **Key Features**

Following is a list of the key features supported for this release.

• Project Navigator

The Project Navigator is the primary window interface used to access all of the Xilinx design tools.

• Design entry tools (Schematic Editor and HDL Editor)

The HDL Editor supports Verilog, VHDL, and ABEL HDL.

Xilinx provides the StateCAD Editor for designing State machines and HDL Bencher Editor for creating test benches. StateCAD and HDL Bencher are Visual Software Solutions, Inc. (VSS) products.

• Design Synthesis

The design synthesis tools create an EDIF netlist for HDL designs. Project Navigator supports two synthesis tools:

- Xilinx Synthesis Tool (XST)

- FPGA Express

• Design Implementation tools

These tools place and route FPGAs or run the fitter for CPLDs. The design implementation tools also create back-annotated files for use in simulation.

• Design Constraints Graphical User Interfaces (GUIs)

The Project Navigator contains three GUIs for creating constraints: the Xilinx Constraints Editor, Floorplanner, and the FPGA Express Constraints Editor.

- Third Party Tools

- Model Technology Incorporated (MTI)

The ISE software supports a variety of simulation tools produced by MTI. Xilinx provides the ModelSim Xilinx Edition (MXE) on a separate CD. Xilinx also supports the use of its software with the MTI PE and EE/SE simulation tools.

• Visual Software Solutions (VSS)

Xilinx also provides HDL Bencher and StateCAD (VSS products). HDL Bencher and StateCAD software are contained on a single CD. HDL Bencher creates test bench files for use with the simulation tools. StateCAD creates state machines.

• Snapshots

When you have successfully run your design through the design process, you can take a snapshot of the design. A snapshot saves all of the files that you have created which includes all of the files that were created during the design processing, that is, design entry, simulation, implementation, and programming.

**Note** Snapshots are not compatible with the Design Manager Flow Engine. Projects created with Foundation ISE software cannot be opened within the Design Manager Flow Engine.

• Error Navigation to Solution Records via the web

Built into the ISE's Project Navigator is the ability to search thousands of solution records found on the Xilinx software support home page from any error. Because the solutions are maintained on the Xilinx support home page, you are guaranteed to have the most up-to-date solutions available. For a detailed description of key features, refer to the Key Features file by selecting Start  $\rightarrow$  Programs  $\rightarrow$  Xilinx Foundation Series ISE 3.1i  $\rightarrow$  Key Features.

### **Architecture Support**

The software supports the following architecture families in this release.

- Spartan<sup>TM</sup>/XL/-II

- Virtex<sup>TM</sup>/-E/-II

- XC9500<sup>TM</sup>/XL/XV

- XC4000<sup>TM</sup>E/L/EX/XL/XLA

### Documentation

Xilinx provides a suite of documentation that includes detailed online help and online software manuals. The online software manuals are provided in both an HTML browser and PDF file formats.

The following online help is available:

- Project Navigator

- VHDL, Verilog and ABEL keywords

- Design entry tools (HDL Editor, Schematic Editor, Symbol Editor, and State Machine Editor)

- Design implementation tools (PROM File Formatter, FPGA Editor, Floorplanner, Hardware Debugger, JTAG Programmer, Flow Engine, Timing Analyzer, Constraints Editor, and LogiBLOX)

- Umbrella help

Online software manuals include the following:

- CORE Generator User Guide

- Constraints Editor Guide

- Development System Reference Guide

- Floorplanner Guide

- FPGA Editor Guide

- Foundation Series ISE 3.1i User Guide

- Foundation Series ISE 3.1i Quick Start Guide

- Hardware Debugger Guide

- Hardware User Guide

- JTAG Programmer Guide

- Libraries Guide

- LogiBLOX Guide

- PROM File formatter Guide

- Synthesis and Simulation Design Guide

- Timing Analyzer Guide

- Synopsys VHDL Reference Guide (PDF only)

- Synopsys Verilog Reference Guide (PDF only)

- XST User Guide

All of these manuals are supplied on the Documentation CD. You can also access these manuals from the Xilinx Web site. The URL is http://toolbox.xilinx.com/docsan

You can also access the online software manuals from the Xilinx Web Site home page (http://www.xilinx.com) as follows:

- 1. Click Service & Support.

- 2. Click Software Manuals.

In addition to the online version of the software manuals, Xilinx also provides PDF versions for printing.

Two hard copy books are also shipped with the software: the *Foundation Series ISE 3.1i Quick Start Guide* and the *Foundation Series ISE Installation Guide and the Release Notes.*

Other manuals include the *MTI Reference Guide* (which resides on the CD that contains the MTI simulation software) as well as the StateCAD, StateBench, and the HDL Bencher User's Guides (which are all located on the CD that contains the StateCAD and HDL Bencher software).

## **Chapter 2**

## Setting Up the Tools

This chapter includes a list of product configurations, general instructions for installing the software, customer support contacts, and licensing information.

For a detailed discussion of installation and licensing, refer to the *Foundation Series ISE 3.1i Installation Guide and Release Notes.*

This chapter contains the following sections:

- "Product Configurations"

- "Installing Software"

- "Customer Service"

- "Technical Support"

### **Product Configurations**

Following is a list of the product configurations for this release.

- Base-Express (DS-FSE-BSX-PC)

- Express (DS-FSE-EXP-PC)

- Elite (DS-FSE-ELI-PC)

All of these configurations contain FPGA Express, StateCAD Xilinx Edition, HDL Bencher Xilinx Edition, and the Modelsim Xilinx Edition (MXE) simulator. If you plan to use these two software tools, then you must license them. Licensing for MXE is relatively straightforward—follow the installation instructions described in the "Installing MXE Software" section.

To license FPGA Express, refer to the *Foundation Series ISE 3.1i Installation Guide and Release Notes.*

### Installing Software

Ensure the optimum use and operation of your new design tools by installing the software on the recommended hardware with sufficient memory (RAM and hard disk "swap" space). If you experience problems with either the installation, operation, or verification of your installation, contact the Xilinx Technical Support hotline. Refer to the "Technical Support" section of this chapter for specifics.

Please refer to the *Foundation ISE 3.1i Installation Guide and Release Notes* for complete details on installation and prerequisites for installation.

### Installing Xilinx Software

This subsection explains how to install the Xilinx software tools from the Xilinx Foundation Series ISE 3.1i CD. Note that this CD also contains the FPGA Express software.

- 1. Select  $\texttt{Start} \rightarrow \texttt{Run}$ . Type d: setup.exe in the Open field of the Run window and click OK. (If your CD-ROM drive is not the "d" drive, substitute the appropriate drive designation.)

- 2. Follow the instructions on the screen to install the software. You will be asked to register the product from the Welcome screen during install. You can register via the web, email, or fax.

In order to register the product, you need to provide the following information:

Product ID

Your product ID number is located on the back of your software CD pack.

- Your name

- Company

- Mailing address

- Phone number

- email address

When you register, Xilinx gives you a Registration ID. You must have the registration ID in order to complete the installation. The installer first installs all of the Xilinx software and then invokes the installer for FPGA Express. Make sure that you install FPGA Express in the default directory indicated. Your FPGA Express synthesis FlexLM license file will be emailed to you. When install is complete, remove the CD.

You may need to reboot your PC to allow the environment variables and path statement to take effect before you can run the design implementation tools. The Install program will inform you if you need to reboot.

### **Installing Documentation**

The documentation CD contains all of the online software manuals that can be viewed in an HTML browser. This CD also contains PDF versions of manuals that can be viewed with the Adobe Acrobat reader.

Installing the documentation is optional, that is, it is not required to run the software.

To install the Xilinx documentation CD, insert the CD and follow the instructions.

# Installing Test Bench, Simulation, and State Machine Software

Two CDs contain the test bench, simulation, and state machine software. In order to complete the Basic Tutorial in Chapter 4, you must install software that is contained on these two CDs unless you have already installed this software previously.

**Note** If you already have installed MTI and VSS versions of the HDL Bencher, Modelsim, and StateCAD, refer to the "Using Other Versions of ModelSim, HDL Bencher, and StateCAD" section.

### Installing MXE Software

This CD contains the ModelSim Xilinx Edition simulator from MTI. You must install a licensed version of Modelsim to complete the basic tutorial in Chapter 4. To install the CD, perform the following steps:

- 1. Insert the ModelSim Xilinx Edition CD.

- 2. Select Start  $\rightarrow$  Programs  $\rightarrow$  Foundation Series ISE 3.1i  $\rightarrow$  Partner Products  $\rightarrow$ Install Modelsim Xilinx Edition.

When you install this software, you are prompted for licensing. Follow the instructions on the screen to license and install the product.

3. Remove the CD when installation is complete.

### Installing HDL Bencher and StateCAD Software

This CD contains the Xilinx editions of HDL Bencher and StateCAD from VSS. The Xilinx editions of these products do not require licenses but do require you to register with VSS and enter ALLSTAR —a password to obtain the full capability of the Xilinx Edition.

- 1. Insert the CD.

- 2. To install the HDL Bencher, select Start  $\rightarrow$  Programs  $\rightarrow$  Foundation Series ISE 3.1i  $\rightarrow$  Partner Products  $\rightarrow$  Install HDL Bencher Xilinx Edition

Follow the instructions on the screen to install the product.

In order to perform the timing simulation in Chapter 4, Basic Tutorial, you must register the HDL Bencher so that you can use it with expanded capabilities. The following procedure explains how to register for a free and permanent upgrade:

- a) Invoke the HDL Bencher by selecting Start  $\rightarrow$  Programs  $\rightarrow$  HDL Bencher 1.02 Xilinx Edition $\rightarrow$  HDL Bencher 1.02 Xilinx Edition.

- b) Select  $\texttt{Help} \rightarrow \texttt{Register For Free Upgrade } \ldots$  which displays the following dialog box.

| egister                                                                                     |            |

|---------------------------------------------------------------------------------------------|------------|

| Click "Get Password" to obtain a<br>password. Enter the password in<br>Enable Free Upgrade. |            |

| Get Pa                                                                                      | assword    |

| Password:                                                                                   |            |

| Enable Fr                                                                                   | ee Upgrade |

c) Click Get Password.

Netscape (or your default browser) displays a registration form.

- d) Enter your name, company, email address, street address, and telephone number.

- e) Click Submit.

You will be sent an email containing a registration password.

- f) When you receive the password, enter it in the Password box and then click Enable Free Upgrade.

- 3. The StateCAD software is not required to perform the Tutorial in Chapter 4. It is included with Foundation ISE to facilitate design entry, debug, and analysis of state machines. StateCAD includes a translation tool for importing designs originally created with the Xilinx Foundation State Editor. StateCAD significantly enhances state machine design through its FSM, and Logic Wizards. StateCAD generates FPGA optimized and error-free HDL. It also detects hundreds of logic errors and warnings upfront, and provides solutions for them before it generates any HDL.

To install the StateCAD software, select Start  $\rightarrow$  Programs  $\rightarrow$  Foundation Series ISE 3.1i  $\rightarrow$  Partner Products  $\rightarrow$  Install StateCAD Xilinx Edition.

Follow the instructions on the screen to install the product.

## Special StateCAD/HDL Bencher Upgrade for Xilinx Users

All Foundation Series ISE users qualify for a \$500 discount on the purchase of complete editions of StateCAD and HDL Bencher. Sales information is available in the Pricing section of the web sites: www.statecad.com, and www.testbench.com.

When ordering, to receive your software, you will be asked to provide your Host ID, which is located in the Help, About dialog box of each product.

# Using Other Versions of ModelSim, HDL Bencher, and StateCAD

You can integrate non-Xilinx Editions of ModelSim, HDL Bencher, and StateCAD with ISE as follows.

1. Within the Project Navigator, select  $\texttt{Edit} \rightarrow \texttt{Preferences}$  and then select the Partners tab.

The following dialog box displays.

| Preferences                            | X      |

|----------------------------------------|--------|

| General Editor Processes Partner Tools |        |

| Locations of Partner Executables       |        |

| Model Tech Simulator:                  |        |

| e_5.3d_XE\win32xoem\ModelSim.exe       | Browse |

| VSS Test Bencher:                      |        |

| c::\BENCH10\tb.exe                     | Browse |

| VSS State Machine Editor:              |        |

| c:\statecad\Sc.exe                     | Browse |

|                                        |        |

|                                        |        |

|                                        |        |

| OK Cancel                              | Арру   |

2. Enter the full path name to each of your tools or browse to the location of the desired executable (that is, ModelSim.exe for the Modeltec simulator, tb.exe for the VSS Test Bencher, and Sc.exe for the VSS State Machine Editor).

## **Customer Service**

For software licensing information, warranty status, shipping, and order management issues, contact Xilinx Customer Service using the information in the following table.

| Country                               | Telephone        | Facsimile        |

|---------------------------------------|------------------|------------------|

| United States and Canada <sup>1</sup> | 1-800-624-4782   | 408-559-0115     |

| United Kingdom <sup>2</sup>           | 01932-333550     | 01932-828521     |

| Belgium <sup>2</sup>                  | 0800 73738       |                  |

| France <sup>2</sup>                   | 0800 918333      |                  |

| Germany <sup>2</sup>                  | 0130 816027      |                  |

| Italy <sup>2</sup>                    | 1677 90403       |                  |

| Netherlands <sup>2</sup>              | 0800 0221079     |                  |

| Other European Locations <sup>2</sup> | (44) 1932-333550 | (44) 1932-828521 |

| Japan                                 | 81 3 3297 9153   | 81 3 3297 9189   |

<sup>1</sup> Mon-Fri, 8:00 am - 5:00 pm Pacific time

<sup>2</sup> Monday-Friday, 9:00 a.m. to 5:30 p.m. United Kingdom time— English speaking only.

If you are an international customer, contact your local sales representative for customer service issues. Refer to the Xilinx web site at http://support.xilinx.com/company/sales/int\_reps.htm for contact information.

A complete list of Xilinx worldwide sales offices is at http:// support.xilinx.com/company/sales/offices.htm.

## **Technical Support**

The following section details how to reach the Xilinx Application Service centers for your area. If you experience problems with the installation or operation of your software, Xilinx suggests that you first go to our http://support.xilinx.com website.

You can also contact the Xilinx Technical Support hotline by phone, email, or fax. When e-mailing or faxing inquiries, provide your complete name, company name, and phone number. The following table gives Worldwide contact information for Xilinx Application Service centers.

| Location              | Telephone                        | Electronic Mail     | Facsimile (Fax)   |

|-----------------------|----------------------------------|---------------------|-------------------|

| North America         | 1-408-879-5199<br>1-800-255-7778 | hotline@xilinx.com  | 1-408-879-4442    |

| United Kingdom        | 44-1932-820821                   | ukhelp@xilinx.com   | 44-1932-828522    |

| France                | 33-1-3463-0100                   | frhelp@xilinx.com   | 33-1-3463-0959    |

| Germany               | 49-89-93088-130                  | dlhelp@xilinx.com   | 49-89-93088-188   |

| Japan                 | local distributor                | jhotline@xilinx.com | local distributor |

| Korea                 | local distributor                | korea@xilinx.com    | local distributor |

| Hong Kong             | local distributor                | hongkong@xilinx.com | local distributor |

| Taiwan                | local distributor                | taiwan@xilinx.com   | local distributor |

| Corporate Switchboard | 1-408-559-7778                   |                     |                   |

## **Chapter 3**

## **Software Overview**

This overview describes the basic concepts and tools of the Foundation Series ISE release. For details on how to use the tools, refer to the "Basic Tutorial" chapter in this manual or the in-depth tutorial on the Web (http://www.support.xilinx.com/ support/techsup/tutorials/).

This chapter contains the following sections.

- "Starting the Foundation Series ISE Software"

- "Project Navigator"

- "Design Entry"

- "Design Synthesis"

- "Design Constraints"

- "Functional Simulation"

- "Design Implementation"

- "Timing Simulation"

- "Device Programming"

### Starting the Foundation Series ISE Software

To start the software, select  $\texttt{Start} \rightarrow \texttt{Programs} \rightarrow \texttt{Foundation}$ Series ISE 3.11  $\rightarrow$  Project Navigator.

## **Project Navigator**

The Project Navigator—the overall project management tool contains the software tools used in the design process. Within the Project Navigator, you can access the following tools: design entry, synthesis, design implementation, device programming tools, and design verification which includes functional and timing simulation as well as static timing analysis.

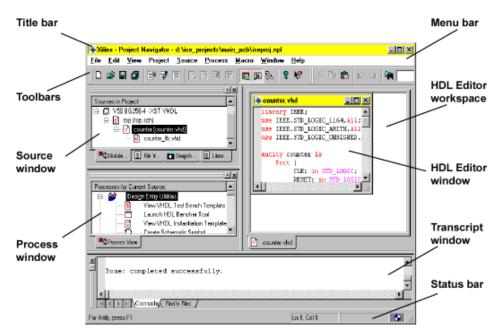

#### Figure 3-1 Project Navigator

The toolbar buttons at the top of the main window provide shortcuts for commonly used commands.

- The Source window contains the source modules for the project.

- The Process window contains the processes that are associated with the selected project source.

- The area located on the right side of the Project Manager is the HDL Editor window.

- The Transcript window at the bottom of the Project Navigator displays informational, warning, and error messages.

- The Status bar displays the status of the current process that is running.

For detailed information about the Project Navigator, refer to the "Project Navigator" chapter in the *Foundation Series ISE 3.1i User Guide*.

### **Project Navigator Online Help**

The Project Navigator contains online help for each of the menu items located in the pulldown menus. You can access the help for these menu items by pressing F1.

For example to access help for the New Source menu item from the Project menu, click the Project menu and then place the cursor on New Source. Press F1 to display the help.

Online help is also available for Project Navigator processes. To access, select a process and press F1.

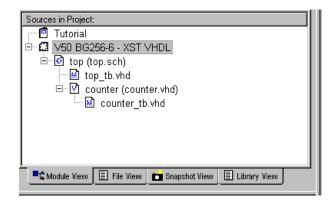

### **Source Window**

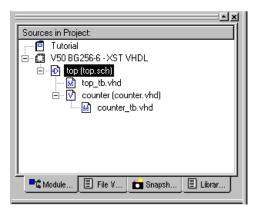

The Source window displays all of the design files associated with a project. A source is any element that contains information about a design. Sources include any files that are needed to describe the behavior of your design: schematics or HDL source files, test files, and design documentation.

The following figure shows an example of a Source window.

Icons represent the various types of source files. To view a complete list of source icons, click the context-sensitive Help icon and then click an unused area of the source window.

Double clicking a source invokes the editor for that source. For example, double clicking a schematic source file invokes the Schematic Editor; the schematic displays within the Schematic Editor tool. Correspondingly, double clicking an HDL file invokes the HDL Editor. When a source file's place in the design hierarchy is modified, the Source window automatically updates to reflect the change. Use the Project pulldown menu or toolbar button to perform the following operations on a source file:

- Create a New Source

- Add a new source to a project

- Copy a source to the current project folder

- Delete Implementation Data

- Archive a project

- Take a snapshot

- Apply Project Properties

### **Process Window**

The Process window displays all the processes that apply for a selected source in the Source window. Processes include synthesis, test bench generation, simulation, implementation, device programming, report generation, or any other logical design step.

The Project Navigator's context-sensitivity automatically determines the design processes for any selected source. The processes are context-sensitive in two ways:

- The processes that display in the Process window depend on the source file that is highlighted in the Source window.

- Some of the processes that display in the Process window differ depending on the device type (FPGA or CPLD).

You run a design process by double clicking a process in the process window. By default the Project Navigator automatically updates outdated processes or reports.

A green check mark next to a process indicates that the process is upto-date and completed without problems. A yellow exclamation point indicates that the process is up-to-date and completed with warnings. A red X indicates that a process failed due to errors.

You can also set properties for many of the processes. To set properties for a process, right click on the process and then select Properties from the menu or select the process and then select **Process**  $\rightarrow$  **Properties**. For a description of all of the Implement Design properties, refer to the "Implementing the Design" chapter in the *Foundation Series ISE 3.1i User Guide*

For a description of the Synthesize properties for XST, see the *XST User Guide*.

### **Transcript Window**

The Transcript window displays all messages, errors, and warnings that result from running processes. You can view this window or hide it by clicking the toolbar button.

When you run a process, messages display in the Transcript window indicating the status of the process. If your design contains synthesis errors or warnings, you can double-click the error or warning message that displays in the Transcript window and the source containing the error is opened. In the source, a red dot displays next to the line containing the error. Alternatively you can right click on the error and navigate to a solution record at support.xilinx.com.

```

Routing: Completed - No errors found.

PAR done.

Starting: 'C:\WINNT\system32\cmd.exe /C call __postpar.bat '

PAR completed successfully

EXEWRAP detected that program '__postpar.bat' completed successfully.

Done: completed successfully.

Console

Find in Files /

Process "implement Design" is up to date.

```

#### Figure 3-2 Transcript Window

In the preceding figure, the Implement Design process has been run and the Transcript window indicates that the last process that ran was PAR (Place and Route --par.bat).

## **Design Entry**

This section describes the design entry tools.

### **HDL Editor**

The ISE language sensitive text editor for HDL includes color coding and context-sensitive help for reserved words. When color coding is enabled, different colored text is used for strings, comments, keywords, and directives. ISE contains language templates so that you can insert existing text structures into your source files.

The "Basic Tutorial" chapter explains how to use the language templates.

The HDL Editor supports Verilog, VHDL, and ABEL. You can customize the Editor's display, input and formatting options.

For details, see the "HDL Sources" chapter in the *Foundation Series ISE 3.11 User Guide*.

### **ECS Schematic Editor**

The ECS (Engineering Capture System) is the Schematic Editor.

The ISE Schematic Editor includes the following features:

- Built-in design rule checking

- VHDL and Verilog structural netlist generation

- Matching symbol generation

For detailed information, refer to the "Schematic Sources" chapter in the *Foundation Series ISE 3.11 User Guide*.

### **Symbol Editor**

You can use the Symbol Editor to create and edit symbols for the Schematic Editor.

Types of symbols that can be created include block symbols and graphic symbols. Block symbols are used to build hierarchical designs.

For detailed information, refer to the "Schematic Sources" chapter in the *Foundation Series ISE 3.1i User Guide*.

### StateCAD and StateBench

The Foundation ISE software includes the Xilinx Edition of StateCAD <sup>®</sup> and StateBench<sup>®</sup> from Visual Software Solutions, Inc. for state machine designs. StateCAD includes a State Machine Wizard to help you develop the initial state machine, a Logic Wizard to create data flow structures, and an Optimization Wizard to maximize performance for the target device.

When installed, StateBench can automatically create VHDL test benches and Verilog test fixtures from StateCAD designs.

Refer to the StateCAD and StateBench online help and documentation for specific information on using these products. For installation information, refer to the "Setting Up the Tools" chapter in this manual or the *Foundation Series ISE 3.1i Installation Guide and Release Notes.*

For information on how to launch the tool, refer to the "State Diagrams" chapter in the *Foundation Series ISE 3.11 User Guide*.

### LogiBLOX and CORE Generator Modules

LogiBLOX is a design tool for creating high-level modules such as counters, shift registers, and multiplexers for FPGA and CPLD designs. LogiBLOX includes both a library of generic modules and a set of tools for customizing these modules. LogiBLOX modules are pre-optimized to take advantage of Xilinx architectural features such as Fast Carry Logic for arithmetic functions and on-chip RAM for dual-port and synchronous RAM. With LogiBLOX, you can create high-level LogiBLOX modules that will fit into your schematic-based design or HDL-based design. For detailed information, refer to the "LogiBLOX" chapter in the *Foundation Series ISE 3.11 User Guide*. Xilinx CORE Generator is a design tool that creates parameterizable cores, optimized for Xilinx FPGAs. The CORE Generator library includes cores as complex as DSP filters and multipliers and as simple as delay elements. You can use these cores as building blocks in order to complete your design more quickly.

For details on how to instantiate cores, refer to the "CORE Generator" chapter in the *Foundation Series ISE 3.1i User Guide*. For complete information about CORE Generator, refer to the online manual, *CORE Generator User Guide*.

## **Design Synthesis**

The Foundation ISE software contains two synthesis tools—XST and FPGA Express. Both synthesis engines accept the same types of input files and then generate the necessary output files so that you can place and route your design. The main difference is that XST can only synthesize designs that are either all VHDL or all Verilog. FPGA Express allows a mixture of both VHDL and Verilog. The following subsections describe each tool.

### XST

You can use XST if designing with the following device families.

- Virtex

- Virtex2

- VirtexE

- Spartan2

- SpartanXL

- XC9500

- XC9500XL

- XC9500XV

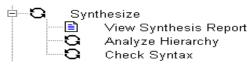

All synthesis processes are placed under a process in the Process window called Synthesize. This process runs the entire synthesis flow to generate the required files so that you can place and route your design. The following diagram illustrates the synthesis flow in the Process window for XST.

You can also set various properties for XST synthesis by right clicking Synthesize and then selecting Properties from the menu. The Process Properties dialog box displays allowing you to select Synthesis Options, HDL Options, and Xilinx Specific Options.

For detailed information about XST, refer to the XST User Guide.

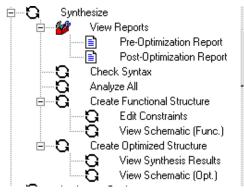

### **FPGA Express**

FPGA Express can synthesize all devices supported for this release.

The Synthesize process runs the complete synthesis flow to produce the necessary files to place and route your design. The following diagram illustrates the synthesis flow in the process window for FPGA Express.

You can examine static timing results with the Express Time Tracker after synthesis and before implementation as follows:

#### Note You must be licensed

(DS-FSE-EXP-PC or DS-FSE-ELI-PC) to use FPGA Express to access the Time Tracker and the Express Constraints Editor.

- 1. Double-click View Synthesis Results in the Process window.

- 2. Select the Paths tab from the Time Tracker to view estimated delays.

# **Design Constraints**

With the design implementation tools, you can control the implementation of a design by entering constraints. There are two basic types of constraints that you can apply to a design: location constraints and timing constraints.

Location constraints control the mapping and positioning of the logic elements in the target device. The most common location constraints are pad constraints. They are used to lock the pins of the design to specific I/O locations so that the pin placement is consistent from revision to revision.

Timing constraints tell the software which paths are critical, and therefore, need closer placement and faster routing. Conversely, timing constraints also tell the software which paths are not critical and, therefore, do not need closer placement or faster routing. Both the placer and the router can be timing constraint driven.

You can enter constraints at various phases of the design process:

- Schematic Editor

- HDL Editor

- UCF file

You can enter constraints manually or with the Xilinx Constraints Editor. Refer to the *Constraints Editor Guide*.

- FPGA Express

- XST constraints file

- Floorplanner

Refer to the Floorplanner Guide for details.

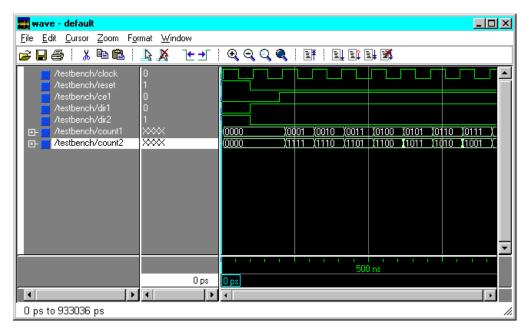

# **Functional Simulation**

Functional Simulation allows you to verify the logic of your design before you synthesize it. You can observe the circuit's behavior at its inputs and outputs as well as the behavior of internal nodes. You can use test benches (VHDL) or test fixtures (Verilog) to specify circuit input stimuli and expected output responses and then test to those specifications prior to synthesis. Foundation ISE supports RTL (Register Transfer Level) simulation as its functional simulation. RTL simulation is performed after design entry but prior to synthesis.

The "Basic Tutorial" chapter has an example of a functional simulation for a counter.

For more detailed information about functional simulation, refer to the "Simulation" chapter in the *Foundation Series ISE 3.11 User Guide*.

# **Design Implementation**

After synthesis is complete, the implementation tools perform the translate map, place, route, (fit for CPLDs), and programming file generation phases of the design flow.

The Process window first step, Translate, merges all of the input netlists. This is accomplished by running NGDBuild. For a complete description of NGDBuild, refer to the "NGDBuild" chapter in the *Development System Reference Guide*.

For FPGAs, the next step is the technology mapper. Map optimizes the gates and trims unused logic in the merged NGD netlist. This step also maps the design's logic resources; logic in the design is mapped to resources on the silicon, and a physical design rule check is performed. For more information about MAP, refer to the "MAP— The Technology Mapper" chapter in the *Development System Reference Guide*.

After the FPGA design is mapped, it is placed and routed. In the place stage, all logic blocks, including the configurable logic blocks (CLB) and input/output blocks (IOB) structures, are assigned to specific locations on the die.

If timing constraints have been placed on particular logic components, the placer tries to meet those constraints by moving the corresponding logic blocks closer together.

In the routing stage, the logic blocks are assigned specific interconnect elements on the die. If timing constraints have been placed on particular logic components, the router tries to meet those constraints by choosing a faster interconnect. For more information about PAR, refer to the "PAR—Place and Route" chapter in the online software document, *Development System Reference Guide*. The CPLD fitter implements designs for the XC9500, XC9500XV, and XC9500XL devices. The fitter outputs several files: fitting report (*design\_name*.rpt), static timing report (*design\_name*.tim), guide file (*design\_name*.gyd, programming file (*design\_name*.jed), and timing simulation database (*design\_name*.nga).

For detailed information about implementing CPLD designs, refer to the Foundation online help.

For more detailed information about design implementation, refer to the "Implementing the Design" chapter in the *Foundation Series ISE 3.11 User Guide*.

### **Interpreting the Reports**

The reports generated by implementation provide information on logic trimming, logic optimization, timing constraint performance, and I/O pin assignment. To access a report, double-click the report in the Process window after you have run your design through design implementation.

#### **Translation Report**

The translation report (.bld) contains warning and error messages from the three translation processes: conversion of the EDIF netlist to the Xilinx NGD netlist format, timing specification checks, and logical design rule checks. The report lists the following:

- Missing or untranslatable hierarchical blocks

- Invalid or incomplete timing constraints

- Output contention, loadless outputs, and sourceless inputs

### Map Report (FPGAs)

The Map Report (.mrp) contains warning and error messages detailing logic optimization and problems in mapping logic to physical resources. The report lists the following information:

- Removed logic. Sourceless and loadless signals can cause a whole chain of logic to be removed. Each deleted element is listed with progressive indentation, so the origins of removed logic sections are easily identifiable; their deletion statements are not indented.

- Logic that has been added or expanded to optimize speed.

• The Design Summary section lists the number and percentage of used CLBs, IOBs, flip-flops, and latches. It also lists occurrences of architecturally-specific resources like global buffers and boundary scan logic.

**Note** The Map Report can be very large. To find information, use key word searches. To quickly locate major sections, search for the string '---', because each section heading is underlined with dashes.

# Pre-Route Static Timing Report (FPGAs Only)

Pre-route static timing reports can be very useful in evaluating timing performance. Although route delays are not accounted for, the logic delays can provide valuable information about the design.

If logic delays account for a significant portion (> 50%) of the total allowable delay of a path, the path may not be able to meet your timing requirements when routing delays are added.

Routing delays typically account for 40% to 60% of the total path delays. By identifying problem paths, you can mitigate potential problems before investing time in place and route. You can redesign the logic paths to use less levels of logic, tag the paths for specialized routing resources, move to a faster device, or allocate more time for the path.

If logic-only-delays account for much less (<35%) than the total allowable delay for a path or timing constraint, then the place-androute software can use very low placement effort levels. In these cases, reducing effort levels allow you to decrease runtimes while still meeting performance requirements.

### Place and Route Report (FPGAs)

The Place and Route Report (.par) contains the following information.

• The overall placer score which measures the "goodness" of the placement. Lower is better. The score is strongly dependent on the nature of the design and the physical part that is being targeted, so meaningful score comparisons can only be made between iterations of the same design targeted for the same part.

- The Number of Signals Not Completely Routed should be zero for a completely implemented design. If non-zero, you may be able to improve results by using re-entrant routing or the multipass place and route flow.

- The timing summary at the end of the report details the design's delays.

# Pad Report (FPGAs)

The Pad Report lists the design's pinout in three ways.

- Signals are referenced according to pad numbers.

- Pad numbers are referenced according to signal names.

- PCF file constraints are listed.

### Asynchronous Delay Report (FPGAs)

This report shows the 20 worst net delays within the design.

### Fitting Report (CPLDs)

The Fitting Report (*design\_name*.rpt) lists summary and detailed information about the logic and I/O pin resources used by the design, including the pinout, error and warning messages, and Boolean equations representing the implemented logic.

# Post Route Timing Report (FPGAs Only)

Post-Route timing reports incorporate all delays to provide a comprehensive timing summary. If a placed and routed design has met all of your timing constraints, then you can proceed by creating programming data and downloading to a device. On the other hand, if you identify problems in the timing reports, you can try fixing the problems by increasing the placer effort level, using re-entrant routing, or using multi-pass place and route. You can also redesign the logic paths to use fewer levels of logic, tag the paths for specialized routing resources, move to a faster device, or allocate more time for the paths.

# Timing Report (CPLDs)

The report is equivalent to the Post Route Timing Report—provides a comprehensive timing summary of all delays.

### Lock Pins Report

The Lock Pins Report is generated by running PIN2UCF. PIN2UCF is a program that generates pin locking constraints in a UCF file by reading a placed NCD file for FPGAs or GYD file for CPLDs. PIN2UCF writes its output to an existing UCF file. If there is no existing UCF file, PIN2UCF creates a new file.

The Lock Pins Report file has two sections: Constraint Conflicts Information and List of Errors and Warnings.

- The Constraints Conflicts Information section does not display if there are fatal input errors, for example, missing inputs or invalid inputs. However, the created report file contains the List of Errors and Warnings.

- The Constraints Conflicts Information section has two subsections:

- Net name conflicts on the pins

- Pin name conflicts on the nets

If there are no conflicting constraints, both subsections under the Constraint Conflicts Information section contain a single line indicating that there are no conflicts.

The List of Errors and Warnings displays only if there are errors or warnings.

For detailed information about PIN2UCF, refer to the "PIN2UCF" chapter in the *Development System Reference Guide*.

# MPPR Report (FPGAs Only)

The MPPR (Multi-Pass Place and Route) report is generated for FPGAs only. MPPR runs iterations of PAR with different cost tables. MPPR scores each PAR iteration and uses the scores to determine the best passes to save. Scores are based on the number of unrouted nets, delays on nets, and timing constraints. For details about MPPR, refer to the "Output from PAR" section in the *Development System Reference Guide*.

# **Other Design Implementation Tools**

This section briefly discusses other design implementation tools.

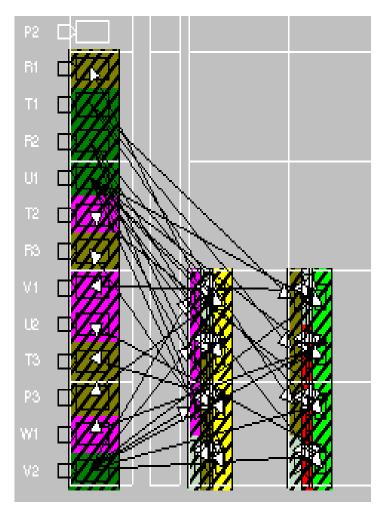

#### Floorplanner (FPGAs)

The Floorplanner is a graphical placement tool that gives you control over placing a design into a target FPGA using a "drag and drop" paradigm with the mouse pointer.

The Floorplanner displays a hierarchical representation of the design in the Design Hierarchy window using hierarchy structure lines and colors to distinguish the different hierarchical levels. The Floorplan window displays the floorplan of the target device into which you place logic from the hierarchy.

Floorplanning is an optional methodology to help you improve performance and density of a fully, automatically placed and routed design. Floorplanning is particularly useful on structured designs and data path logic. With the Floorplanner, you see where to place logic in the floorplan for optimal results, placing data paths exactly at the desired location on the die.

With the Floorplanner, you can floorplan your design prior to or after running PAR. In an iterative design flow, you floorplan and place and route, interactively. You can modify the logic placement in the Floorplan window as often as necessary to achieve your design goals. You can save the iterations of your floorplanned design to use later as a constraints file for MAP.

For detailed information about the Floorplanner, refer to the *Floorplanner Guide*.

#### **FPGA Editor**

The FPGA Editor is a graphical application for displaying and configuring Field Programmable Gate Arrays (FPGAs). You can use this application to place and route critical components before running the automatic place and route tools on your design. You can also use the FPGA Editor to manually finish placement and routing if the routing program does not completely route your design. The FPGA Editor requires a Native Circuit Description (NCD) file. This file contains the logic of your design mapped to components (such as CLBs and IOBs). In addition, the FPGA Editor reads from and writes to a Physical Constraints File (PCF).

For detailed information about the FPGA Editor, refer to the *FPGA Editor Guide*.

#### Post Fit ChipViewer (CPLDs)

You can use the ChipViewer to display a graphical representation of how the logic circuitry and I/Os are assigned to the CPLD macrocells and pins.

# **Timing Simulation**

For Foundation ISE, timing simulation is a *gate-level* simulation that includes detailed timing information for the targeted device. Gate-level simulation is performed after synthesis and place and route.

You can run timing simulation by creating a test bench file with HDL Bencher graphically (no scripting required) or by modifying a template file (View VHDL or Verilog Test Bench Template).

# **Device Programming**

This section explains how the bitstream file is created for FPGAs and CPLDs, and also describes which tools to use for downloading a bitstream to a device.

# **Create Programming File (FPGAs)**

Double clicking Create Programming File runs BitGen. BitGen translates the physical implementation into a programming file (bit) that is used to program the FPGA. The BitGen executable creates the programming file. To set options, right click Create Programming Files and then select Properties to display the Process Properties dialog box.

For more information about the BitGen executable, refer to the "BitGen" chapter in the online software manual, *Development System Reference Guide*.

# Viewing Programming File Generation Report (FPGAs)

This report contains information about the BitGen run.

### **PROM File Formatter (FPGAs)**

An FPGA or daisy chain of FPGAs can be configured from serial or parallel PROMs. The PROM File Formatter can create MCS, EXO, or TEK style files. The files are read by a PROM programmer that turns the image into a PROM.

A HEX file can also be used to configure an FPGA or a daisy chain of FPGAs through a microprocessor. The file is stored as a data structure in the microprocessor boot-up code.

### Hardware Debugger (FPGAs)

The Hardware Debugger can download a BIT file or a PROM file: MCS, EXO, or TEK file formats. A BIT file contains configuration information for an FPGA device. For more information on using the Hardware Debugger, see the *Hardware Debugger Guide*.

### **JTAG Programmer**

For CPLDs, you generate the bitstream file by first highlighting the Part Number Flow Type line in the Sources window and then doubleclick on the JTAG Programmer process. You can then download the bitstream from your PC using the JTAG Programmer.

The JTAG Programmer software can be used to configure both FPGAs and CPLDs and supports both the XChecker and the Parallel Cable III. This is a GUI based program. See the *JTAG Programmer Guide* for details. Also, see the *Hardware User Guide* for information about cable compatibility.

# **Chapter 4**

# **Basic Tutorial**

This basic tutorial describes how to use the VHDL and schematic design entry tools, explains how to perform functional and timing simulation, and describes how to implement a design. For an indepth explanation of the ISE design tools, see the in-depth tutorial on the Xilinx web site (http://www.support.xilinx.com/support/techsup/tutorials/).

The chapter contains the following sections.

- "Introduction"

- "Online Help"

- "Hints"

- "Design Entry (VHDL)"

- "Functional Simulation"

- "Design Entry (Top-Level Schematic)"

- "Design Implementation"

- "Timing Simulation"

# Introduction

This tutorial accomplishes the following:

- Provides some helpful tips on how to use the Schematic Editor

- Describes how to create a VHDL module for a 4-bit counter

- Explains how to use the ISE simulation tools to perform a functional simulation of the 4-bit counter

- Describes how to create a schematic symbol for the VHDL module 4-bit counter

- Illustrates how to create a top-level schematic and instantiate VHDL modules into the schematic

- Explains how to use the Schematic Editor to wire the components together, add net names to the wires, create buses, and add I/O markers

- Describes how to implement the design and view the placed and routed design in the Floorplanner

- Explains how to perform a timing simulation of the top-level design.

# **Online Help**

F1-On-Line Help is available and is context sensitive. For example, if you are using the Schematic Editor to add wires, press F1 to display help on adding wires.

# Hints

The following subsections provide some useful tips about the Source and Process windows as well as the Schematic Editor.

# **Source and Process Windows**

The Process window shows the processes that can be performed on the source selected in the Source window. The list of processes changes according to the type of source that is selected.

For example, to make a schematic symbol for a VHDL module, select the VHDL module in the Source window and then double-click the Create Schematic Symbol process in the Design Entries Utilities branch in the Process window.

# **Schematic Editor Tips**

The following subsections provide some useful tips for using the Schematic Editor. To open the Schematic Editor, perform the following steps.

- 1. Select  $Project \rightarrow New Source...$

- 2. Select Schematic from the list box. Enter a name in the File Name box.

- 3. Select Next.

- 4. Select Finish.

#### **General Object-Action vs. Action-Object**

The Schematic Editor is designed so that you can select the action you wish to perform followed by the object the action is to be performed on (action-object). In general, most Windows applications currently operate by selecting the object and then the action to be performed on that object (object-action). The following subsections illustrate how the action-object model works.

#### **Dragging a Net Name**

When dragging a net name, select  $\texttt{Edit} \rightarrow \texttt{Drag}$  and then place the cursor on the wire associated with the net name in the center of the net name as shown in the figure below.

| • |   |   |   | • |     |   |   |   |   |   | - |   |   |   |   |     |   |   |   |   |   |   |              |    |   |    |     |    |   |

|---|---|---|---|---|-----|---|---|---|---|---|---|---|---|---|---|-----|---|---|---|---|---|---|--------------|----|---|----|-----|----|---|

| : | : | : | : | : | : : | : | : | : | 2 | : |   |   | : |   | : | : : |   |   | 2 | : |   | : | Γ            |    |   |    |     |    |   |

| : | 1 | : | 1 | : | : : | : | : | : | 1 | : |   |   | : | 1 |   | : : | ÷ | 1 | 1 | • | • | • | c            | ΥĽ | L | 1  | : : |    | : |

| ÷ | ÷ | ÷ | ÷ | : | • • | : | ÷ | ÷ | ÷ | ÷ |   |   | ÷ | ÷ | ÷ | : : | Ξ | · | ÷ | · | ÷ | · | È            |    | ė | à  | _   | T. | ÷ |

|   | · | · |   |   |     |   |   |   |   |   |   |   |   |   |   |     | - |   |   |   |   |   | 17           |    | 2 | 20 | -   |    |   |

|   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |              |    |   |    |     |    |   |

|   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   | $\mathbb{P}$ | 1  | _ |    |     |    |   |

| ÷ | ÷ | · | ÷ | ÷ |     |   |   |   |   |   | ! |   |   |   | ÷ | : : | • | • | • | • |   | • | E            |    | R |    |     |    | ÷ |

| • | : | · | : | : |     |   | · |   |   |   | ! | • |   |   |   |     | • | • | • |   |   |   | E            |    | R |    |     |    | : |

Figure 4-1 Dragging a Net Name

#### Adding a Net Name to an I/O Wire

To add net names to wires that are I/Os, perform the following steps.

- 1. Extend the length of each I/0 using Add  $\rightarrow$  Wire.

- 2. Select Add → Net Name and position the cursor at the end of the wire when placing the net name as shown in the following figure.

Figure 4-2 Adding a Net Name

- 3. Type the net name and press Enter.

- 4. Click the end of the wire to place the net name.

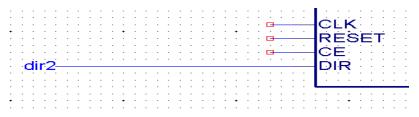

#### Adding I/O Markers

To add I/O markers, perform the following steps.

- 1. Select  $Add \rightarrow I/O$  Marker.

- 2. Select the type of marker and either click the end of the wire or click and drag around a number of I/O wires to place the I/O markers.

|   |          |  | <br>  | L |   |   |   |   |   |   |   | IC. | F  |    |   |  |

|---|----------|--|-------|---|---|---|---|---|---|---|---|-----|----|----|---|--|

|   | dir2     |  |       |   |   | ٠ |   |   |   |   |   | Ϋ́  | ÷  |    |   |  |

|   | -ldir2-> |  |       |   |   |   |   |   |   |   |   | D   | ŀF | Ş. |   |  |

|   |          |  | <br>• |   |   |   |   |   |   |   |   | 2   | Υ. | 2  |   |  |

| ÷ |          |  | <br>• |   | ÷ |   | · | ÷ | · | · | · | ١.  |    |    | ÷ |  |

Figure 4-3 Adding I/O Markers

# **Design Entry (VHDL)**

This section explains how to create a 4-bit counter module using the Language Templates.

#### Starting the ISE Software

To start ISE, select  $\texttt{Start} \rightarrow \texttt{Programs} \rightarrow \texttt{Foundation}$  Series ISE  $\texttt{3li} \rightarrow \texttt{Project}$  Navigator from the Start menu.

#### **Creating a New Project**

The following steps explain how to create a new project.

1. Select File  $\rightarrow$  New Project.... The New Project dialog box displays.

| rw Project                        |                             |                   |

|-----------------------------------|-----------------------------|-------------------|

| Project name:                     | Project Local<br>O:\Example |                   |

| Project Device Options:<br>Proper | rty Name                    | Value             |

| Device Family                     | -                           | Spatian           |

| Device                            |                             | S05 PC84-4        |

| Synthesis Tool                    |                             | FPGA Express VHDL |

#### Figure 4-4 New Project Dialog Box

- 2. In the Project Location field, browse to the directory under which you want to create your new project directory. There is a browse button next to the Project Location field.

- 3. Create a new project by entering "Tutorial" in the Project Name field. When you enter "Tutorial" in the Project Name field, a Tutorial directory is automatically created in the directory path in the Project Location field. For example, for the directory path D:\My Projects, entering the Project Name Tutorial modifies the path to be D:\My Projects\Tutorial.

- 4. Use the pulldown arrow to enter the Value for each Property Name.

There is a pulldown arrow in each Value field. However, you cannot see the arrow until you click in the field.

Change the Values as follows:

- Device Family: Virtex

- Device: V50 BG256-6

- Synthesis Tool: XST VHDL

- 5. Click **OK**. Foundation ISE creates a subdirectory and a new project.

# **Creating a 4-Bit Counter Module**

Use the Language Templates to create a VHDL module for a counter as follows:

- 1. Select  $Project \rightarrow New Source...$

- 2. Select VHDL Module as the source type and give it a file name "counter".

- 3. Click Next.

- 4. Click Next.

- 5. Click **Finish** to complete the new source file template. An editor window displays showing the library declaration and use statements along with the entity and architecture pair for the counter.

- Open the Language Templates by selecting Edit → Language Templates or by clicking the light bulb icon located on the far right on the toolbar.

- 7. In the Language Templates window, click the + sign next to VHDL and then click the + sign next to Synthesis Templates.

- Click and drag the Counter template from the VHDL → Synthesis Templates folder to the counter architecture between the begin and end behavioral statements. Close the Language Template.

| V Language Templates                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|